Issue: Jul. 13, 2012

# Specifications for

# TFT-LCD Monitor

Version 1.0

MODEL COM33T3N71ZLC

|                                        | JOINIOUT CITT ILLO                                    |

|----------------------------------------|-------------------------------------------------------|

|                                        |                                                       |

| Customer's Approval                    |                                                       |

| Signature:                             |                                                       |

| Name:                                  |                                                       |

| Section:                               |                                                       |

| Title:                                 |                                                       |

| Date:                                  |                                                       |

|                                        |                                                       |

| DRUSTEC                                |                                                       |

|                                        |                                                       |

|                                        |                                                       |

|                                        |                                                       |

| ORTUS TECHNOLOGY CO., LTD. Sales Dept. | ORTUS TECHNOLOGY CO., LTD.  Product Quality Assurance |

| Approved by                            | Approved by                                           |

| 7. Tamera                              | n. Konya                                              |

| Checked by                             | Checked by                                            |

|                                        | E. Takale                                             |

|                                        |                                                       |

Prepared by

# (2/45) Issue: Jul. 13, 2012 SPECIFICATIONS № 12TLM041 Version History Page Description Ver. Date Jul. 13, 2012 First issue 1.0

(3/45)

| SPECI | FICΔ      | TIONS | No 12 | TI MOA        |

|-------|-----------|-------|-------|---------------|

|       | 1 1 1 1 7 |       | 1 1 2 | 1 1 1 1 1 1 1 |

Issue: Jul. 13, 2012

# Contents

| 1. | Application                                           | <br>4  |

|----|-------------------------------------------------------|--------|

| 2. | Outline Specifications                                |        |

|    | 2.1 Features of the Product                           | <br>5  |

|    | 2.2 Display Method                                    | <br>5  |

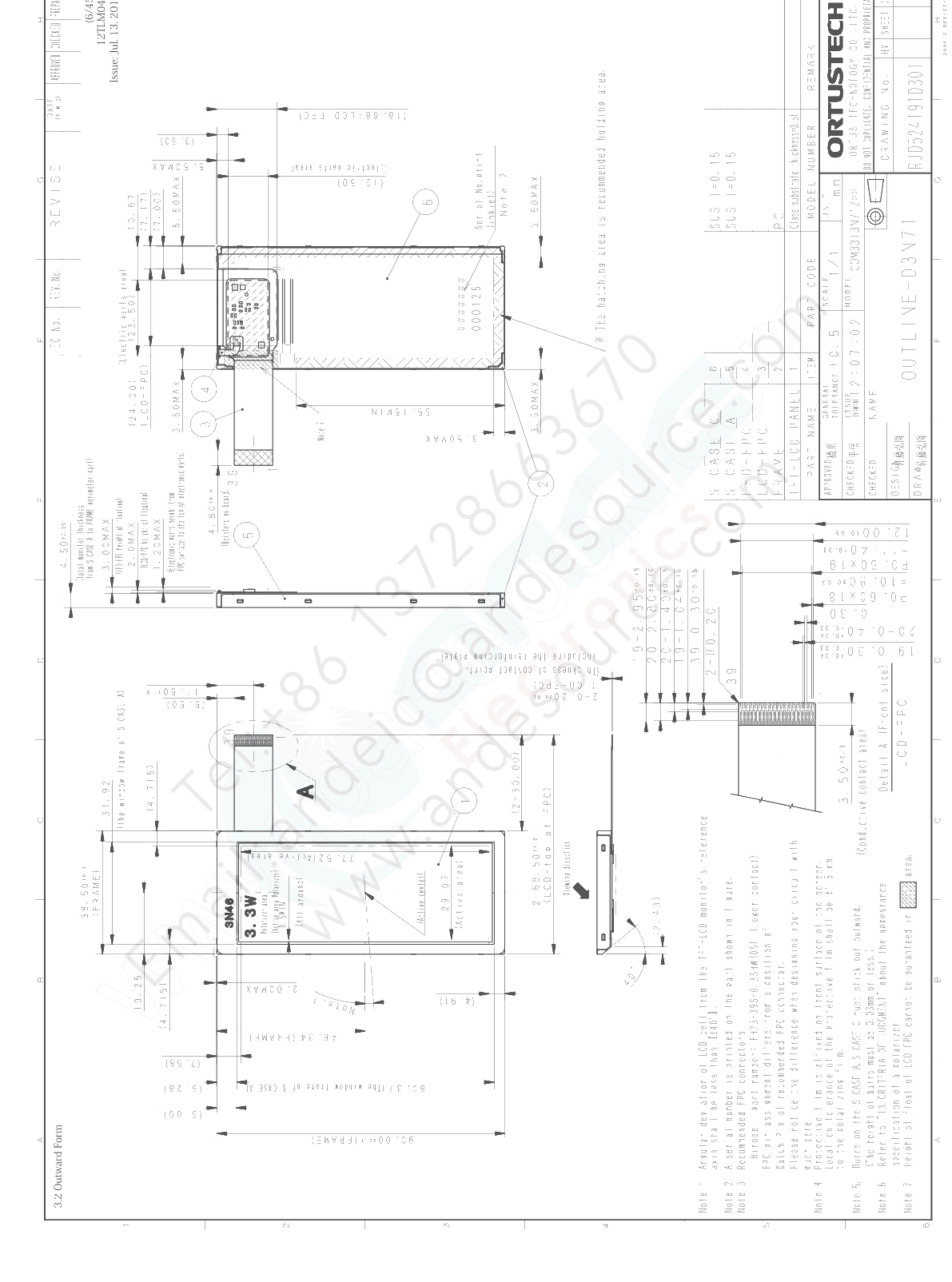

| 3. | Dimensions and Outward Form                           |        |

|    | 3.1 Dimensions                                        | <br>5  |

|    | 3.2 Outward Form                                      | <br>6  |

|    | 3.3 Serial Label (S-LABEL)                            | <br>7  |

| 4. | Pin Assignment                                        | <br>8  |

| 5. | Absolute Maximum Rating                               | <br>9  |

| 6. | Recommended Operating Conditions                      | <br>9  |

| 7. | Characteristics                                       |        |

|    | 7.1 DC Characteristics                                | <br>10 |

|    | 7.2 Reset Timing Characteristics                      | <br>11 |

|    | 7.3 AC Characteristics                                | <br>11 |

|    | 7.4 Input Timing Characteristics                      | <br>13 |

|    | 7.5 Input Timing Chart                                | <br>14 |

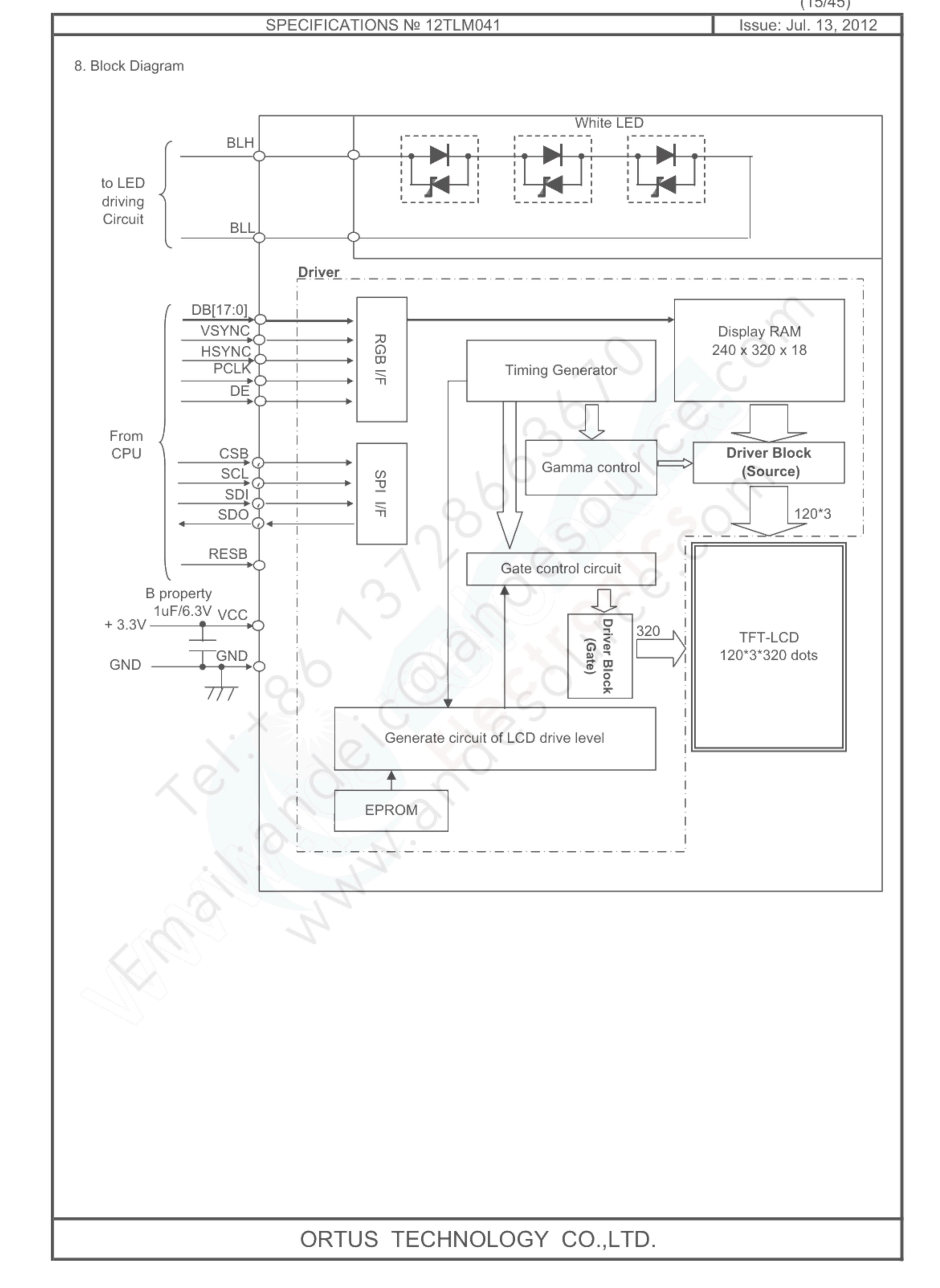

| 8. | Block Diagram                                         | <br>15 |

| 9. | Interface                                             |        |

|    | 9.1 RGB Interface                                     | <br>16 |

|    | 9.2 Serial Interface                                  | <br>16 |

| 0. | Driving Description                                   |        |

|    | 10.1 Registers List                                   | <br>18 |

|    | 10.2 GRAM Address                                     | <br>22 |

|    | 10.3 RGB <=> Internal Clock Operation                 | <br>23 |

|    | 10.4 Update Still Picture Area in Moving Picture Mode | <br>24 |

| 1. | Sequence                                              |        |

|    | 11.1 Power-ON Sequence                                | <br>25 |

|    | 11.2 Power-OFF / Standby Sequence                     | <br>27 |

|    | 11.3 Standby Release Sequence                         | <br>27 |

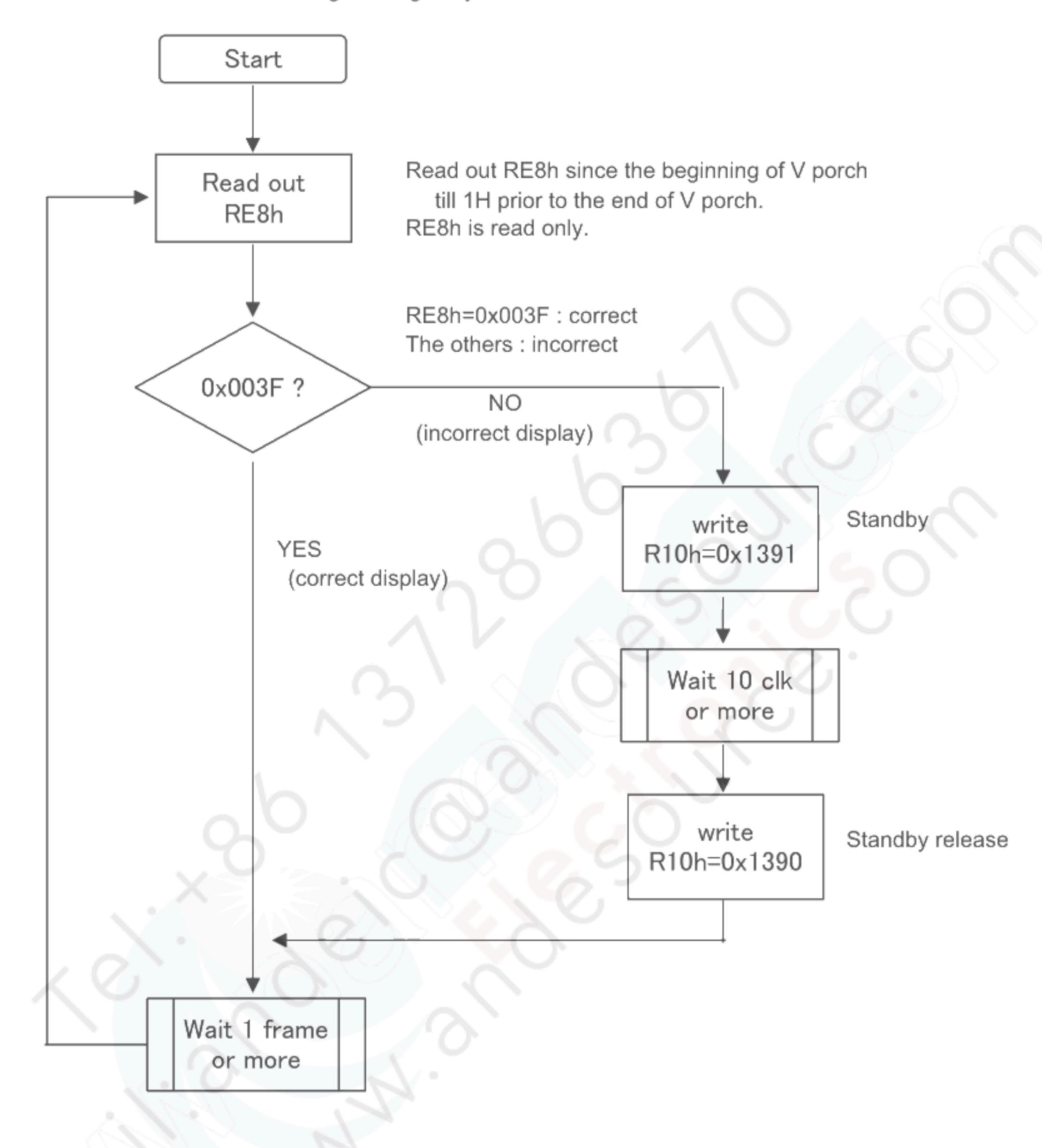

|    | 11.4 Refresh Sequence 1                               | <br>29 |

|    | 11.5 Refresh Sequence 2                               | <br>31 |

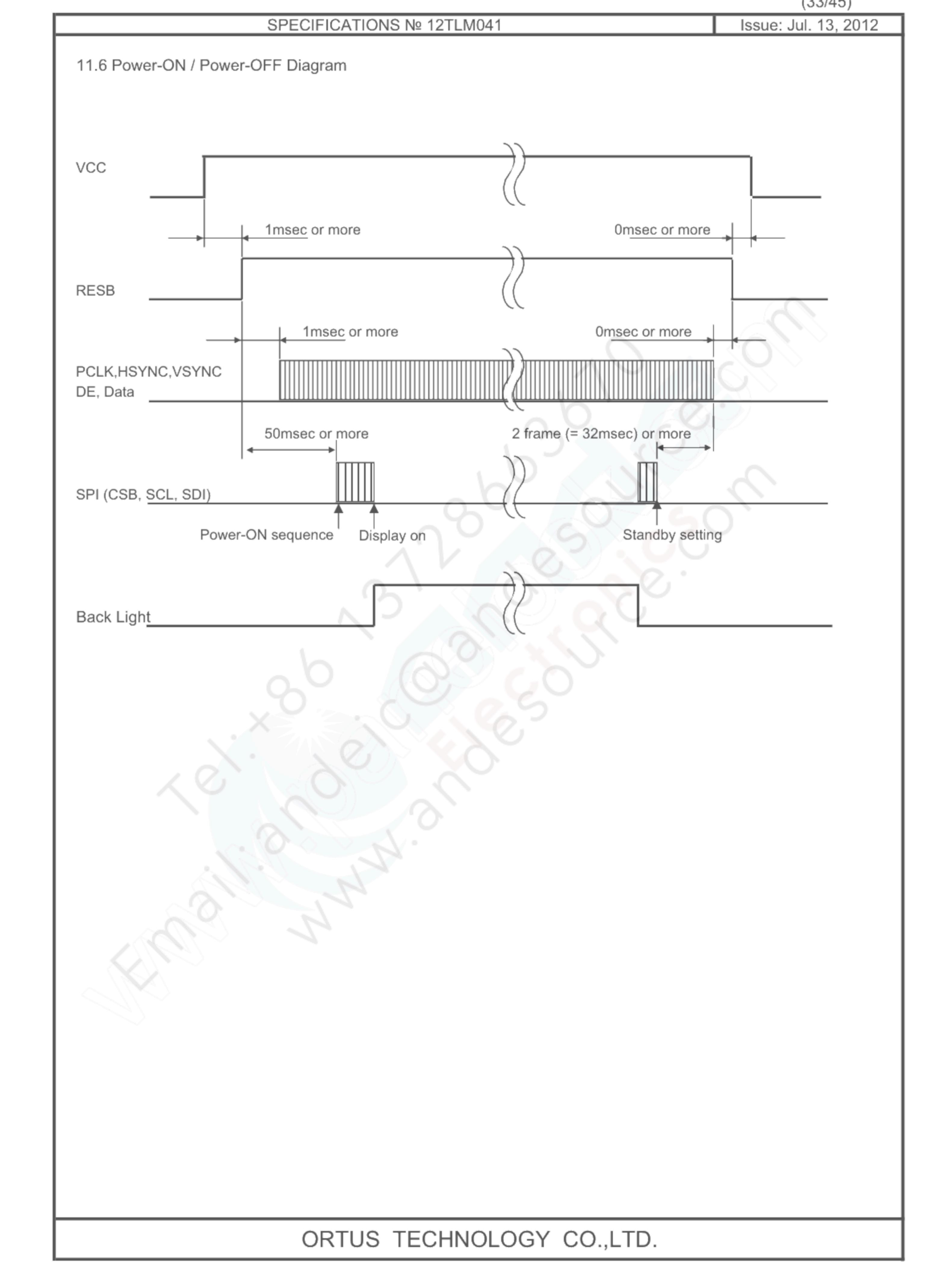

|    | 11.6 Power-ON / Power-OFF Diagram                     | <br>33 |

| 2. | Characteristics                                       |        |

|    | 12.1 Optical Characteristics                          | <br>34 |

|    | 12.2 Temperature Characteristics                      | <br>35 |

| 3. | Criteria of Judgment                                  |        |

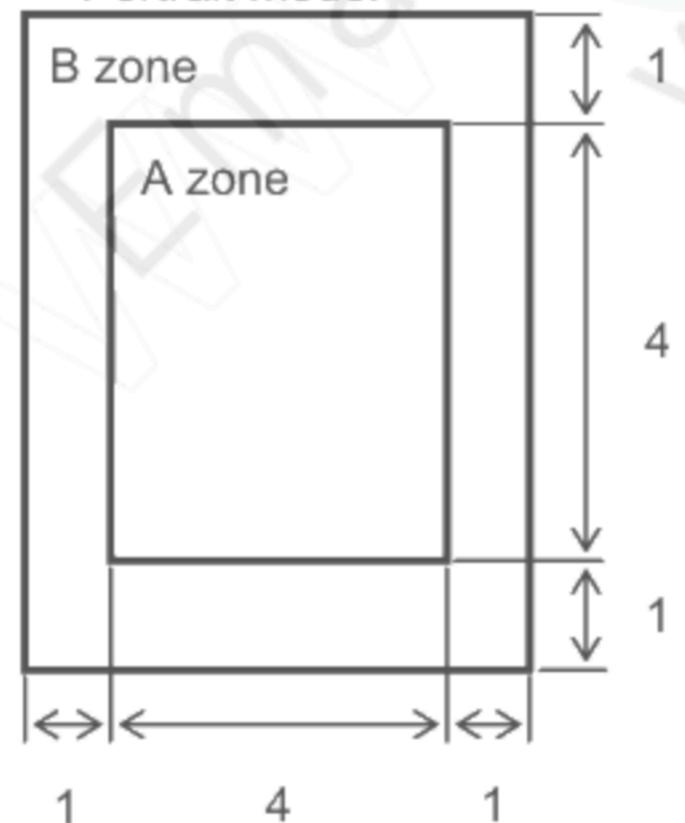

|    | 13.1 Defective Display and Screen Quality             | <br>36 |

|    | 13.2 Screen and Other Appearance                      | <br>37 |

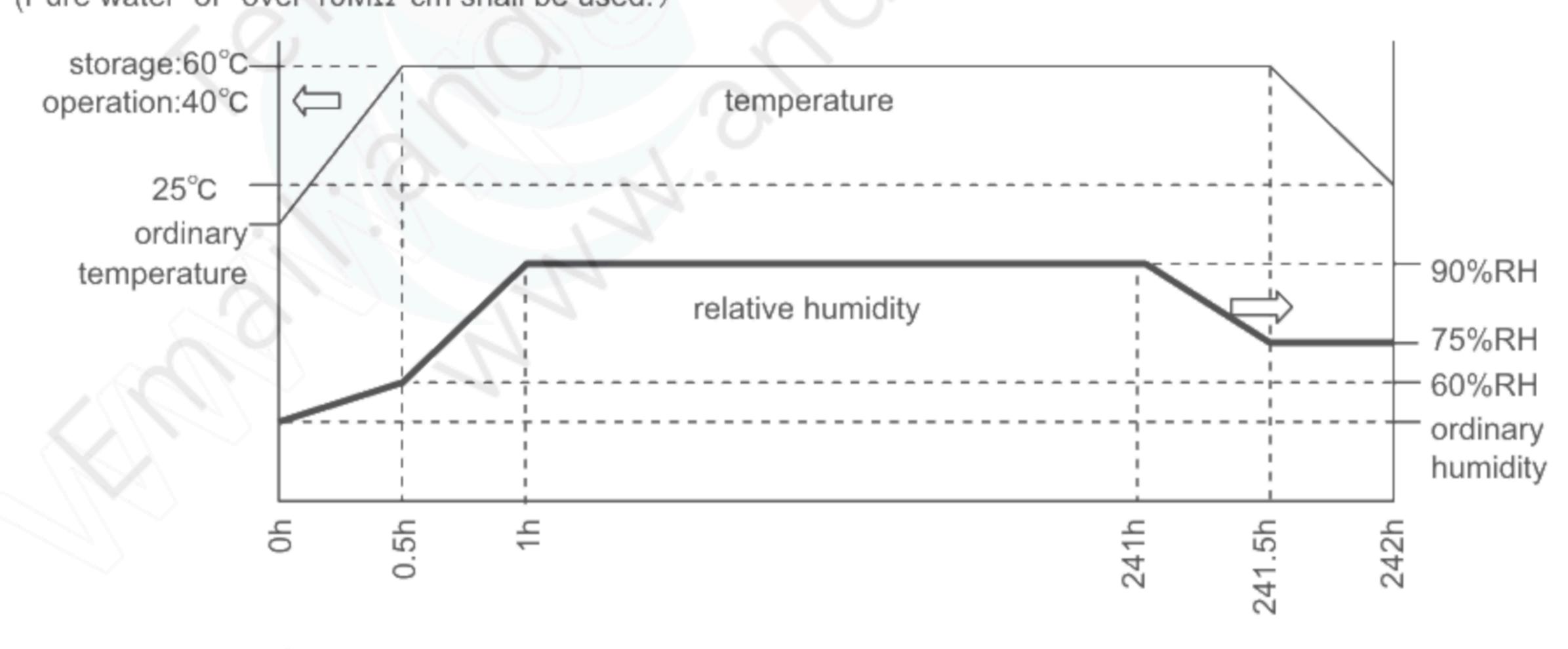

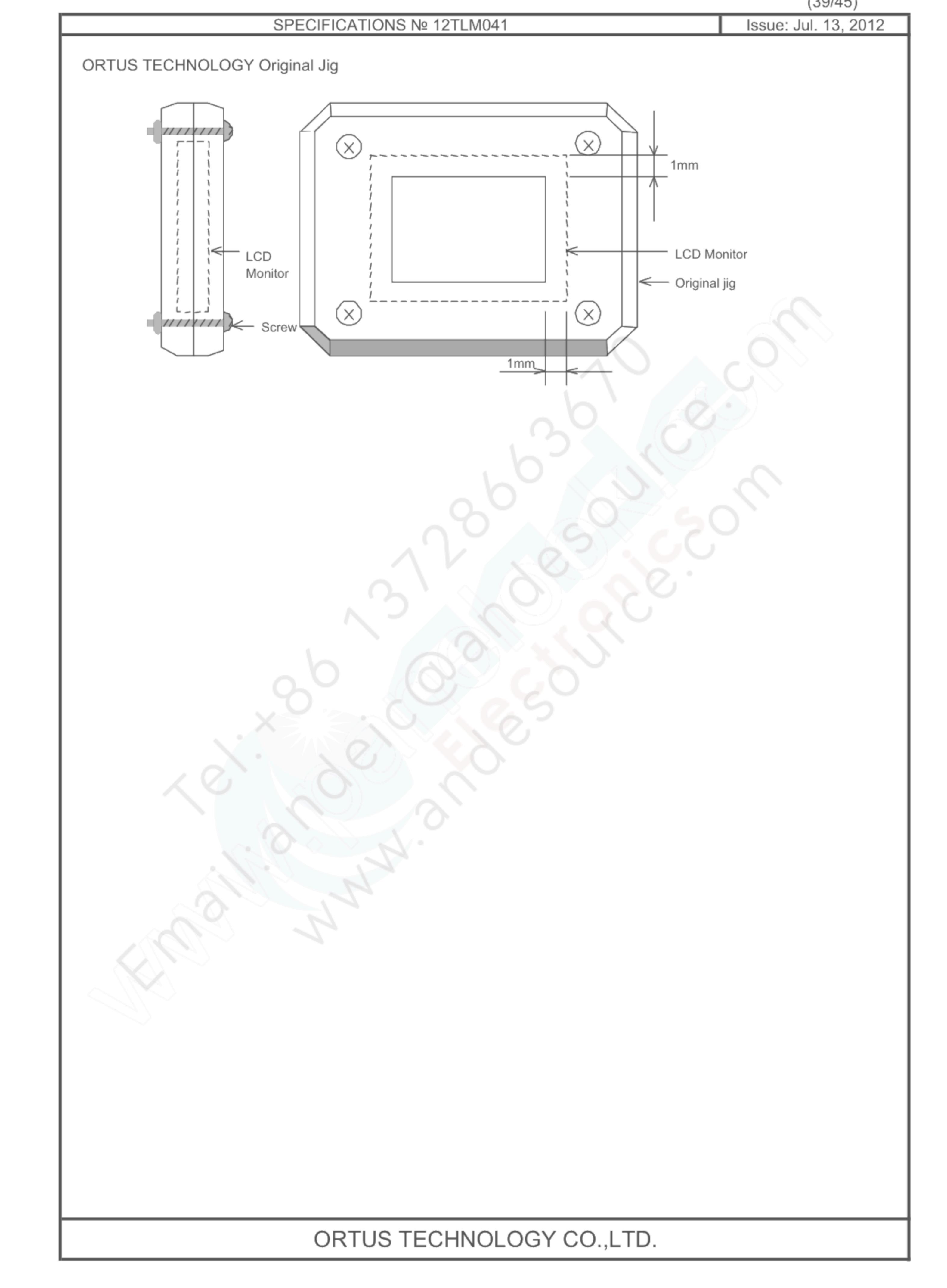

| 4. | Reliability Test                                      | <br>38 |

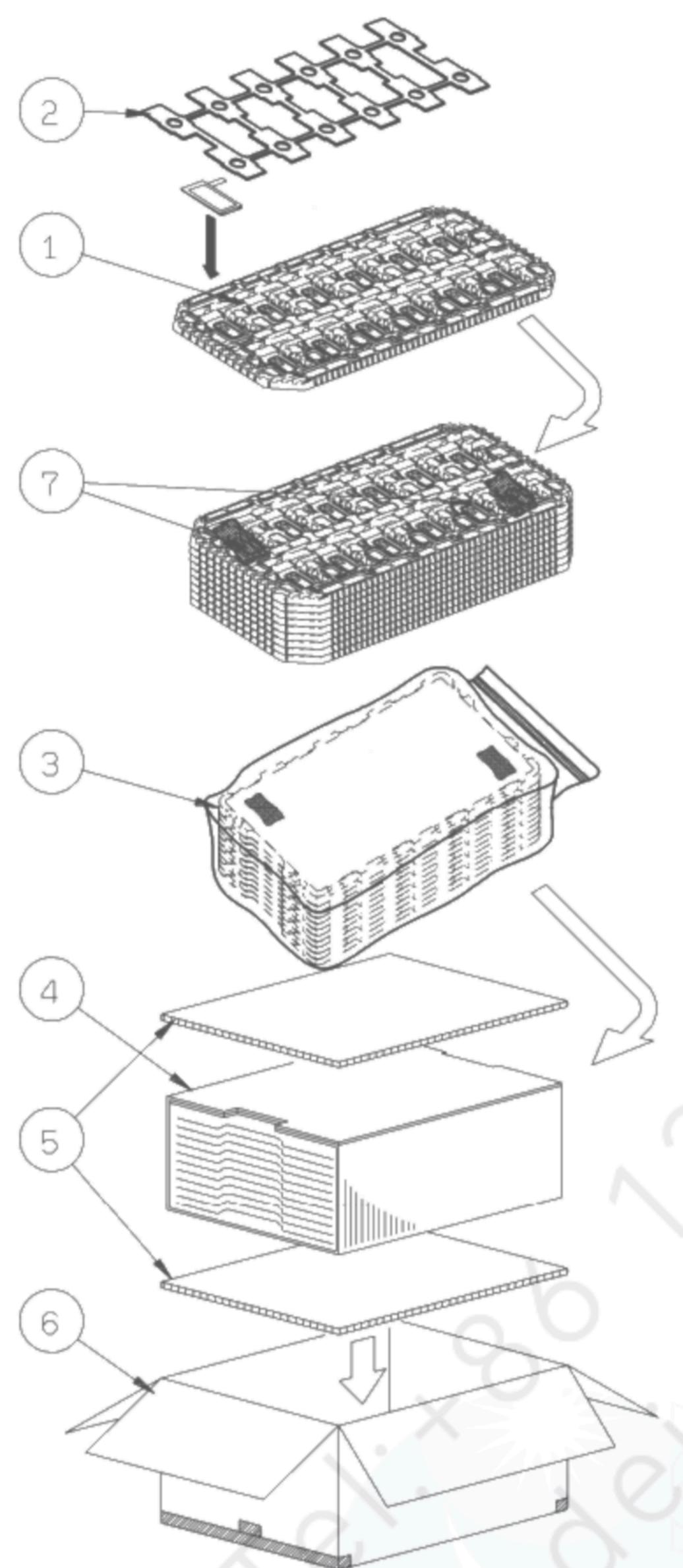

| 5. | Packing Specifications                                | <br>40 |

| 6. | Handling Instruction                                  |        |

|    | 16.1 Cautions for Handling LCD panels                 | <br>41 |

|    | 16.2 Precautions for Handling                         | <br>42 |

|    | 16.3 Precautions for Operation                        | <br>42 |

|    | 16.4 Storage Condition for Shipping Cartons           | <br>43 |

|    | 16.5 Precautions for Peeling off the Protective film  | <br>43 |

| -  |                                                       |        |

| Δ  | PPFNDIX                                               | <br>44 |

#### SPECIFICATIONS № 12TLM041

Issue: Jul. 13, 2012

# Application

This Specification is applicable to 8.28cm (3.3 inch) TFT-LCD monitor for non-military use.

- ORTUS TECHNOLOGY makes no warranty or assume no liability that use of this Product and/or any information including drawings in this Specification by Purchaser is not infringing any patent or other intellectual property rights owned by third parties, and ORTUS TECHNOLOGY shall not grant to Purchaser any right to use any patent or other intellectual property rights owned by third parties. Since this Specification contains ORTUS TECHNOLOGY's confidential information and copy right, Purchaser shall use them with high degree of care to prevent any unauthorized use, disclosure, duplication, publication or dissemination of ORTUS TECHNOLOGY'S confidential information and copy right.

- ① If Purchaser intends to use this Products for an application which requires higher level of reliability and/or safety in functionality and/or accuracy such as transport equipment (aircraft, train, automobile, etc.), disaster-prevention/security equipment or various safety equipment, Purchaser shall consult ORTUS TECHNOLOGY on such use in advance.

- This Product shall not be used for application which requires extremely higher level of reliability and/or safety such as aerospace equipment, telecommunication equipment for trunk lines, control equipment for nuclear facilities or life-support medical equipment.

- ORTUS TECHNOLOGY assumes no liability for any damage resulting from misuse, abuse, and/or miss-operation of the Product deviating from the operating conditions and precautions described in the Specification.

- ① If any issue arises as to information provided in this Specification or any other information, ORTUS TECHNOLOGY and Purchaser shall discuss them in good faith and seek solution.

- ORTUS TECHNOLOGY assumes no liability for defects such as electrostatic discharge failure occurred during peeling off the protective film or Purchaser's assembly process.

This Product is compatible for RoHS directive.

| Object substance                                   | Maximum content [ppm] |

|----------------------------------------------------|-----------------------|

| Cadmium and its compound                           | 100                   |

| Hexavalent Chromium Compound                       | 1000                  |

| Lead & Lead compound                               | 1000                  |

| Mercury & Mercury compound                         | 1000                  |

| Polybrominated biphenyl series (PBB series)        | 1000                  |

| Polybrominated biphenyl ether series (PBDE series) | 1000                  |

SPECIFICATIONS № 12TLM041

Issue: Jul. 13, 2012

# 2. Outline Specifications

#### 2.1 Features of the Product

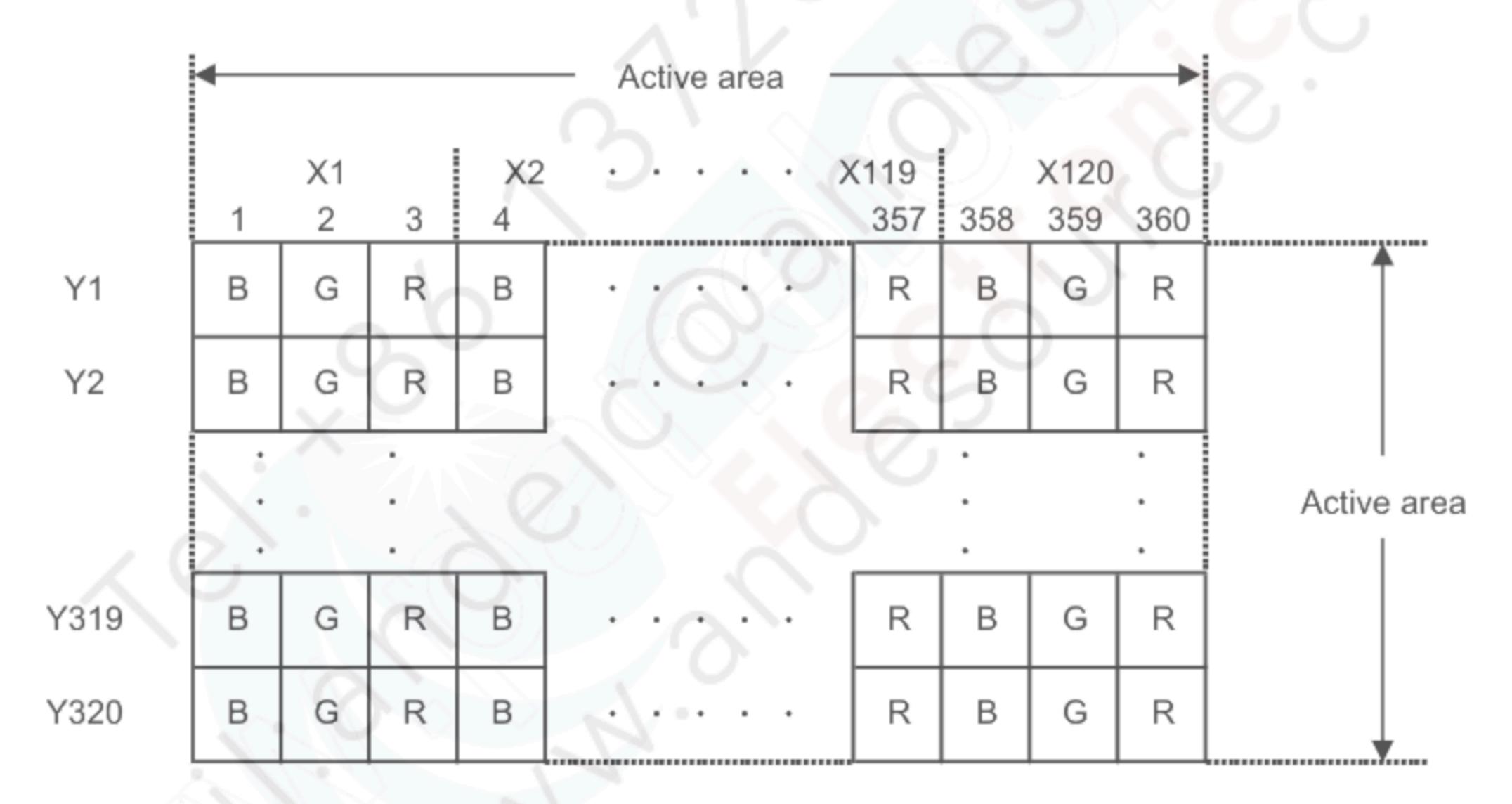

- 3.3 inch diagonal display, 120 x RGB [H] x 320 [V] dots.

- 262,144 / 65,536 colors.

- Single power supply operation of 3.3V.

- Timing generator [TG], Counter-electrode driving circuitry, Built-in power supply circuit.

- Power save (Standby) mode capable.

- Long life & High bright white LED back-light.

# 2.2 Display Method

| Items               | Specifications                       | Remarks                    |

|---------------------|--------------------------------------|----------------------------|

| Display type        | TN type 262,144 or 65,536 colors.    |                            |

|                     | Transmissive type, Normally white    |                            |

| Driving method      | a-Si TFT Active matrix.              |                            |

|                     | Line-scanning, Non-interlace.        |                            |

| Dot arrangement     | RGB stripe arrangement.              | Refer to "Dot arrangement" |

| Signal input method | Data: 18-bit / 16-bit RGB interface. |                            |

|                     | Command : SPI interface.             |                            |

| Backlight type      | Long life & High bright white LED.   |                            |

| Viewing direction   | 3:00 (Right)                         |                            |

Dot arrangement (FPC cable placed right side)

#### 3. Dimensions and Outward Form

#### 3.1 Dimensions

| Items              | Specifications              | Unit | Remarks               |

|--------------------|-----------------------------|------|-----------------------|

| Outline dimensions | 38.5[H] × 90.0[V] × 4.50[D] | mm   | Exclude FPC cable and |

|                    |                             |      | parts on FPC.         |

| Active area        | 29.07[H] × 77.52[V]         | mm   | 8.28cm diagonal       |

| Number of dots     | 360[H] × 320[V]             | dot  |                       |

| Dot pitch          | 80.75[H] × 242.25[V]        | um   |                       |

| Weight             | 26.4                        | g    | Include FPC cable     |

Issue: Jul. 13, 2012

# 3.3 Serial No. print (S-print)

# 1) Display Items

S-print indicates the least significant digit of manufacture year (1digit), manufacture month with below alphabet (1letter), model code (4characters), serial number (6digits).

\* Contents of Display

| * | * | **** | ***** |

|---|---|------|-------|

| _ | - |      |       |

| а | b | С    | d     |

|   | Contents of display                             |                   |               |       |  |       |  |  |

|---|-------------------------------------------------|-------------------|---------------|-------|--|-------|--|--|

| а | The least significant digit of manufacture year |                   |               |       |  |       |  |  |

| b | Manufacture month                               | Jan-A May-E Sep-I |               |       |  |       |  |  |

|   |                                                 | Feb-B             |               | Jun-F |  | Oct-J |  |  |

|   |                                                 | Mar-C             |               | Jul-G |  | Nov-K |  |  |

|   |                                                 | Apr-D             |               | Aug-H |  | Dec-L |  |  |

| С | Model code                                      | 33SC              | (Made in Japa | n)    |  |       |  |  |

|   |                                                 | 33TC              | (Made in Mala | ysia) |  |       |  |  |

|   |                                                 | 33VC              | (Made in Mala | ysia) |  |       |  |  |

| d | Serial number                                   |                   |               |       |  |       |  |  |

<sup>\*</sup> Example of indication of Serial No. print (S-print)

2J33SC000125

means "manufactured in October 2012, 3.3" S type, C specifications, serial number 000125"

Made in Malaysia

2J33TC000125

means "manufactured in October 2012, 3.3" T type, C specifications, serial number 000125"

· Made in China

2J33VC000125

means "manufactured in October 2012, 3.3" V type, C specifications, serial number 000125"

2) Location of Serial No. print (S-print)

Refer to 3.2 "Outward Form".

3)Others

Please note that it is likely to disappear with an organic solvent about the Serial print.

<sup>·</sup>Made in Japan

# Issue: Jul. 13, 2012

# 4. Pin Assignment

| No. | Symbol | Function                                                               |

|-----|--------|------------------------------------------------------------------------|

| 1   | BLL    | LED drive power source. (Cathode side)                                 |

| 2   | BLH    | LED drive power source. (Cathode side)                                 |

| 3   | TEST1  | Open                                                                   |

| 4   | VCC    | Power supply input.                                                    |

| 5   | VCC    | Power supply input.                                                    |

| 6   | VSYNC  | Vertical sync signal input. (Negative polarity at VSPL=0)              |

| 7   | HSYNC  | Horizontal sync signal input. (Negative polarity at VOI L-0)           |

| 8   | PCLK   | Clock input for display. (Data Input on the rising edge at DPL=0)      |

| 9   | DE     | Input data effective signal. (Lo: active at EPL=0.)                    |

| 10  | GND    | Ground                                                                 |

| 11  | RESB   | System reset signal input. (Lo: active)                                |

| 12  | GND    | Ground                                                                 |

| 13  | RDB    | Connect to VCC.                                                        |

| 14  | RS     | Connect to VCC.                                                        |

| 15  | GND    | Ground                                                                 |

| 16  | GND    | Ground                                                                 |

| 17  | DB17   | Display data input for (R).                                            |

| 18  | DB16   | 00h for black display                                                  |

| 19  | DB15   | DB12:LSB DB17:MSB                                                      |

| 20  | DB14   |                                                                        |

| 21  | DB13   |                                                                        |

| 22  | DB12   |                                                                        |

| 23  | DB11   | Display data input for (G).                                            |

| 24  | DB10   | 00h for black display                                                  |

| 25  | DB9    | DB6:LSB DB11:MSB                                                       |

| 26  | DB8    |                                                                        |

| 27  | DB7    |                                                                        |

| 28  | DB6    |                                                                        |

| 29  | DB5    | Display data input for (B).                                            |

| 30  | DB4    | 00h for black display                                                  |

| 31  | DB3    | DB0:LSB DB5:MSB                                                        |

| 32  | DB2    |                                                                        |

| 33  | DB1    |                                                                        |

| 34  | DB0    |                                                                        |

| 35  | SDI    | Data input for serial communication.                                   |

| 36  | SDO    | Data output for serial communication. (If not use, leave it open.)     |

| 37  | CSB    | Chip select input for serial communication. (Lo: active)               |

| 38  | SCL    | Clock input for serial communication. (Data Input on the rising edge.) |

| 39  | GND    | Ground                                                                 |

- Recommended connector: HIROSE ELECTRIC [FH23-39S-0.3SHW(05)]

- Please make sure to check a consistency between pin assignment in "3.2 Outward Form" and your connector pin assignment when designing your circuit.

Inconsistency in input signal assignment may cause a malfunction.

(9/45)

# SPECIFICATIONS № 12TLM041

Issue: Jul. 13, 2012

# Absolute Maximum Rating

GND=0V

| Item                    | Symbol | Condition      | Rating                   |          | Unit | Applicable terminal       |

|-------------------------|--------|----------------|--------------------------|----------|------|---------------------------|

|                         |        |                | MIN                      | MAX      |      |                           |

| Supply voltage          | VCC    |                | -0.3                     | 4.6      | V    | VCC                       |

| Input voltage for logic | VI     |                | -0.3                     | VCC+0.3  | V    | VSYNC,HSYNC,PCLK,DE,      |

|                         |        |                |                          |          |      | DB[17:0],CSB,SCL,SDI,RESB |

| Forward current         | IL     |                |                          | 60.0     | mA   | BLH - BLL                 |

| Storage temperature     | Tstg   |                | -30                      | 80       | °C   |                           |

| range                   |        |                |                          |          |      |                           |

| Storage humidity range  | Hstg   | Non condensi   | sing in an environmental |          |      |                           |

|                         |        | moisture at or | less than 40 °C          | C 90%RH. |      |                           |

# 6. Recommended Operating Conditions

GND=0V

| Item                          | Symbol | Condition |                                                                          | Rating | Rating |    | Applicable terminal                                   |

|-------------------------------|--------|-----------|--------------------------------------------------------------------------|--------|--------|----|-------------------------------------------------------|

|                               |        |           | MIN                                                                      | TYP    | MAX    |    |                                                       |

| Supply voltage                | VCC    |           | 3.0                                                                      | 3.3    | 3.6    | V  | VCC                                                   |

| Input voltage for logic       | VI     |           | 0                                                                        |        | VCC    | V  | VSYNC,HSYNC,PCLK,<br>DE,DB[17:0],CSB,<br>SCL,SDI,RESB |

| Operational temperature range | Тор    | Note1,2   | -20                                                                      | +25    | +70    | °C | Panel surface temperature                             |

| Operating humidity range      | Нор    | Ta<=40 °C | 20                                                                       |        | 85     | %  |                                                       |

|                               | 0      | Ta>40 °C  | Non condensing in an environmental moisture at or less than 40 °C 85%RH. |        |        |    |                                                       |

Note1: This monitor is operable in this temperature range. With regard to optical characteristics, refer to Item 12."CHARACTERISTICS".

(10/45)

#### SPECIFICATIONS № 12TLM041

Issue: Jul. 13, 2012

#### Characteristics

#### 7.1 DC Characteristics

# 7.1.1 Display Module

(Unless otherwise noted, Ta=25 °C, VCC=3.3V, GND=0V)

| (Offices officed, ra-25 C, vCC-5.5v, Grab-0v) |        |                                   |         |        |         |                     |                                           |  |  |

|-----------------------------------------------|--------|-----------------------------------|---------|--------|---------|---------------------|-------------------------------------------|--|--|

| Item                                          | Symbol | Condition                         |         | Rating | Unit    | Applicable terminal |                                           |  |  |

|                                               |        |                                   | MIN     | TYP    | MAX     |                     |                                           |  |  |

| Input Signal<br>Voltage                       | VIH    | VCC=3.0-3.6V                      | 0.8×VCC |        | VCC     | ٧                   | VSYNC,HSYNC,<br>PCLK,DE,<br>DB[17:0],CSB, |  |  |

|                                               | VIL    |                                   | 0       |        | 0.2×VCC | V                   | SCL,SDI,RESB                              |  |  |

| Operating<br>Current                          | ICC    | Color bar display                 |         | 7.5    | 15.0    | mA                  | VCC                                       |  |  |

| Standby<br>Current                            |        | Other input with constant voltage |         | 25     | 50      | uA                  | VCC                                       |  |  |

7.1.2 Backlight

| 7.11.2 Daokiiş  | 9111   |                     |        |          |      | 1//  |                     |

|-----------------|--------|---------------------|--------|----------|------|------|---------------------|

| Item            | Symbol | Condition           | Rating |          |      | Unit | Applicable terminal |

|                 |        |                     | MIN    | TYP      | MAX  |      |                     |

| Forward current | IL25   | Ta=25 °C            |        | 35.0     | 50.0 | mA   | BLH - BLL           |

| Forward voltage | VL     | Ta=25 °C, IL=35.0mA | 7.5    | 8.6      | 9.9  | V    |                     |

| Estimated Life  | LL     | Ta=25 °C            | 1      | (50,000) | )    | hr   |                     |

| of LED          |        | IL=35.0mA           |        | (50,000) |      |      |                     |

Note: - The lifetime of the LED is defined as a period till the brightness of the LED decreases to the half of its initial value.

- This figure is given as a reference purpose only, and not as a guarantee.

- This figure is estimated for an LED operating alone.

As the performance of an LED may differ when assembled as a monitor together with a TFT panel due to different environmental temperature.

- Estimated lifetime could vary on a different temperature and usually higher temperature could reduce the life significantly.

(11/45)

# SPECIFICATIONS № 12TLM041

# Issue: Jul. 13, 2012

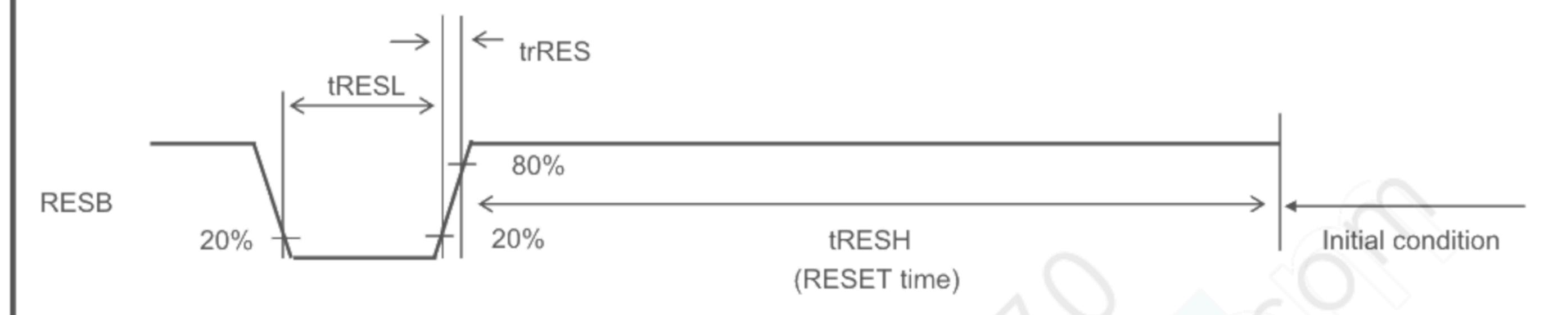

# 7.2 Reset Timing Characteristics

(Unless otherwise noted, Ta=25 °C, VCC=3.3V, GND=0V)

|                    |        |           |     |        |     |      | ,                   |

|--------------------|--------|-----------|-----|--------|-----|------|---------------------|

| Item               | Symbol | Condition |     | Rating |     | Unit | Applicable terminal |

|                    |        |           | MIN | TYP    | MAX |      |                     |

| RESB Low period    | tRESL  |           | 1   |        |     | ms   | RESB                |

| Signal Rising time | trRES  |           |     |        | 10  | us   |                     |

| RESB Hi period     | tRESH  |           | 50  |        |     | ms   |                     |

# 7.3 AC Characteristics

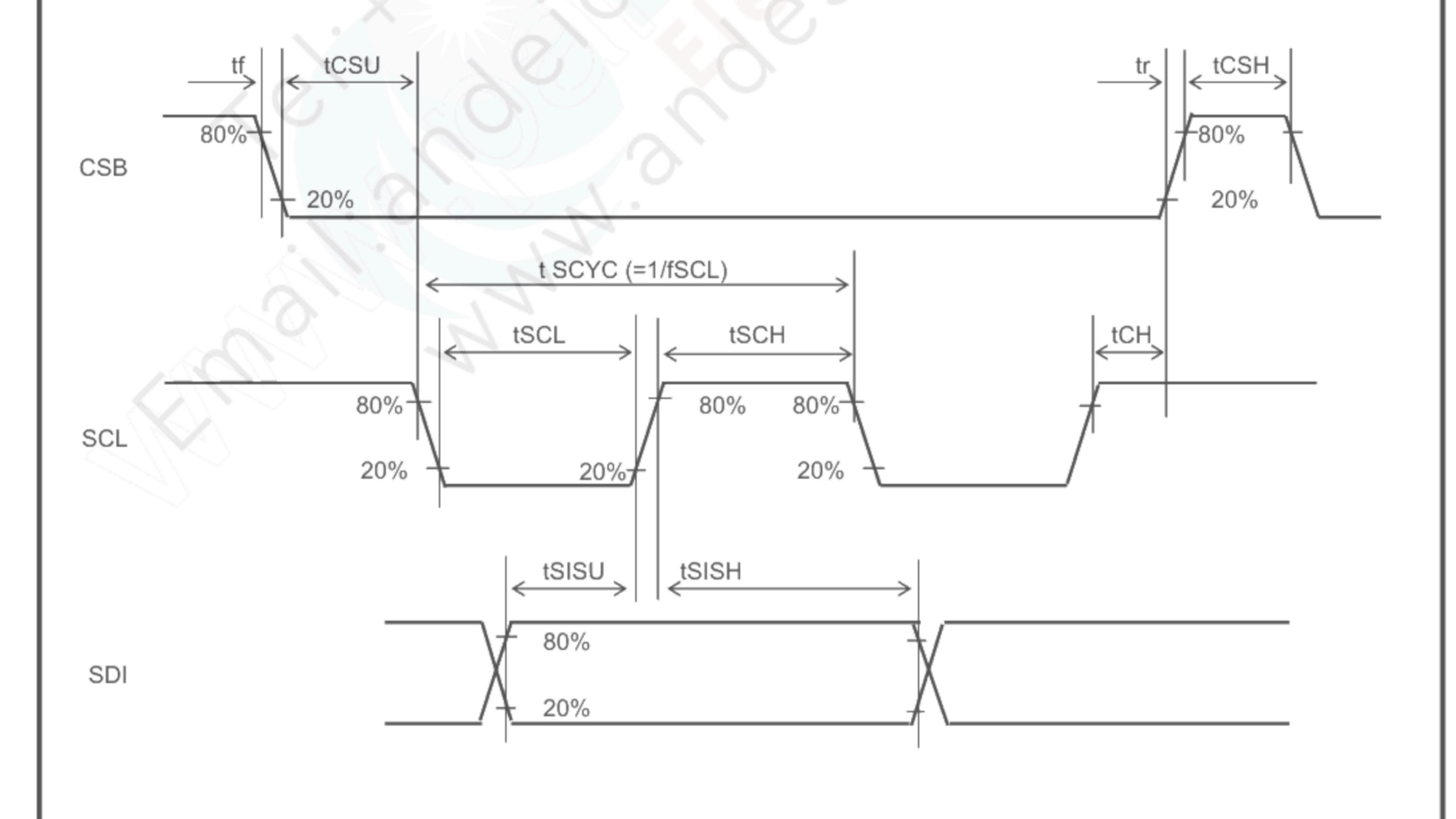

#### 7.3.1 Serial Interface

(Unless otherwise noted, Ta=25 °C, VCC=3.3V, GND=0V)

|                       |        |           |          | Offices Offic | Wisc Hoteu, | 14-20 | 0,000-0.00,010-00)  |

|-----------------------|--------|-----------|----------|---------------|-------------|-------|---------------------|

| Item                  | Symbol | Condition | 1        | Rating        |             | Unit  | Applicable terminal |

|                       |        |           | MIN      | TYP           | MAX         |       |                     |

| Signal Rising time    | tr     |           | J        |               | 10          | ns    | CSB,SCL,SDI         |

| Signal Falling time   | tf     |           | <b>U</b> |               | 10          | ns    |                     |

| CSB setup time        | tCSU   |           | 10       | 0             |             | ns    | CSB                 |

| CSB hold time         | tCH    |           | 50       |               |             | ns    |                     |

| CSB pulse High period | tCSH   | ()        | 100      | )             |             | ns    |                     |

| SDI setup time        | tSISU  |           | 20       | 0             |             | ns    | SDI                 |

| SDI hold time         | tSISH  |           | 20       |               |             | ns    |                     |

| SCL Frequency         | fSCL   |           | 0.7      | 77            | 10          | MHz   | SCL                 |

| SCL pulse Low period  | tSCL   |           | 40       |               |             | ns    |                     |

| SCL pulse High period | tSCH   |           | 40       |               |             | ns    |                     |

(12/45)

Issue: Jul. 13, 2012

#### SPECIFICATIONS № 12TLM041

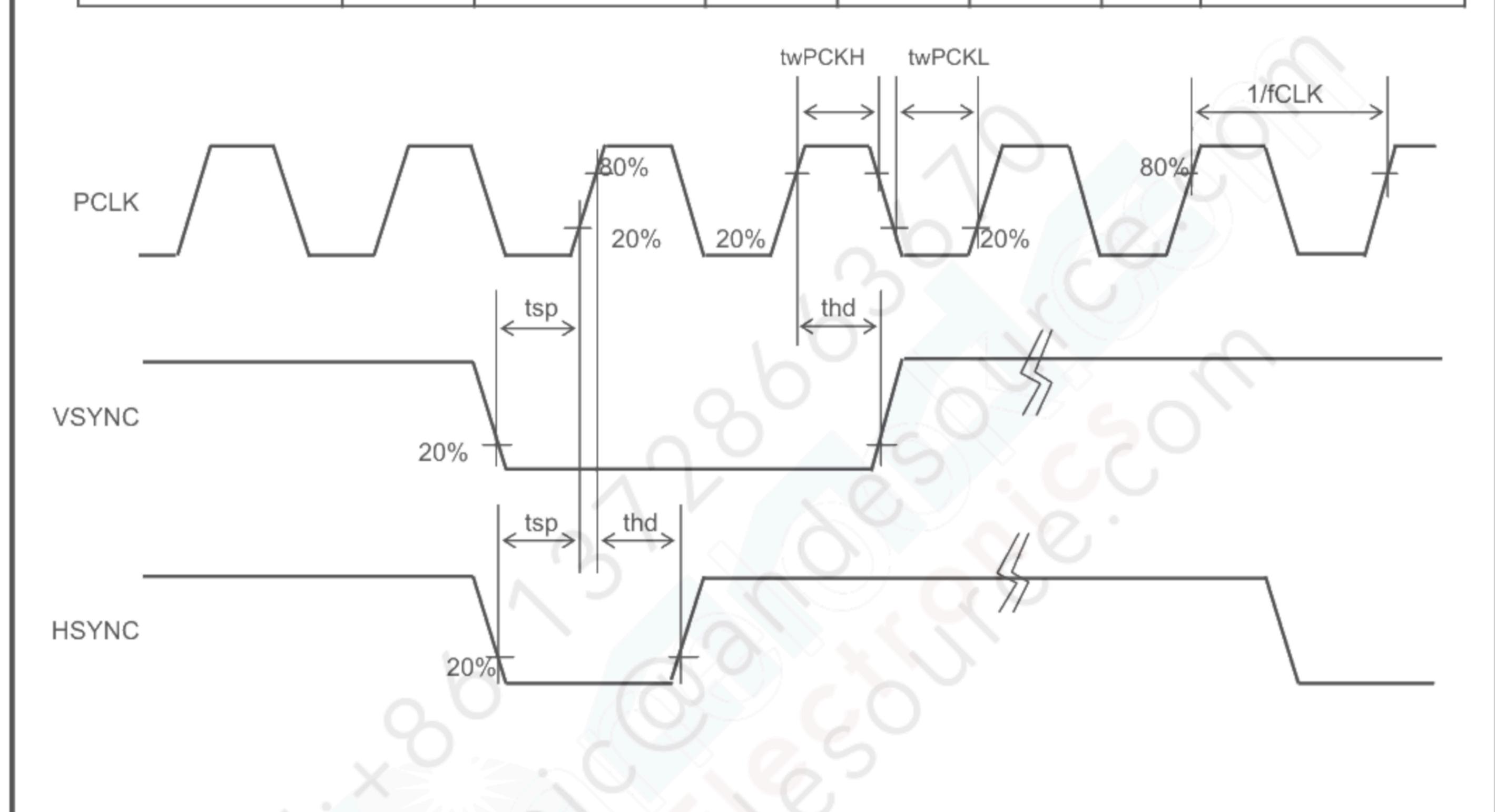

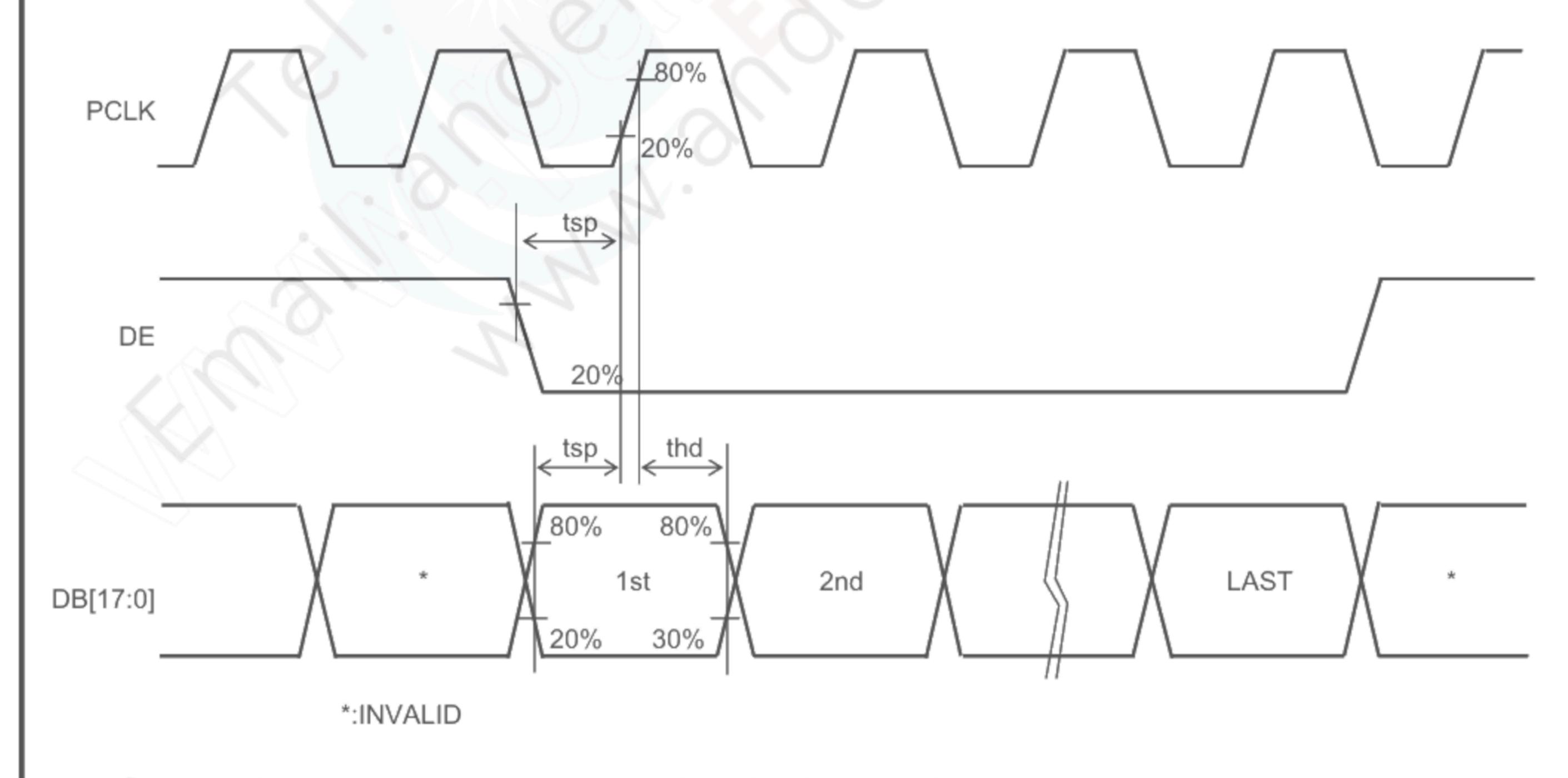

# 7.3.2 RGB Interface

(Unless otherwise noted, Ta=25 °C, VCC=3.3V, GND=0V)

| Item             | Symbol | Condition       | Rating |     |     | Unit | Applicable terminal      |

|------------------|--------|-----------------|--------|-----|-----|------|--------------------------|

|                  |        |                 | MIN    | TYP | MAX |      |                          |

| PCLK Frequency   | fCLK   |                 |        | 5.0 | 6.6 | MHz  | PCLK                     |

| PCLK Low period  | twPCKL | 0.2×VCC or less | 40     |     |     | ns   |                          |

| PCLK High period | twPCKH | 0.8×VCC or more | 40     |     |     | ns   |                          |

| Setup time       | tsp    |                 | 10     |     |     | ns   | PCLK,VSYNC,<br>HSYNC,DE, |

| Hold time        | thd    |                 | 40     |     |     | ns   | DB[17:0]                 |

Case: Interface signal polarity setting Register (R0Fh): VSPL= 0, HSPL= 0, EPL= 0 and DPL= 0.

(13/45)

# SPECIFICATIONS № 12TLM041

Issue: Jul. 13, 2012

# 7.4 Input Timing Characteristics

| Item                      |      | Symbol |     | Rating |      | Unit | Applicable terminal |

|---------------------------|------|--------|-----|--------|------|------|---------------------|

|                           |      |        | MIN | TYP    | MAX  |      |                     |

| PCLK Frequency            |      | fPCLK  |     | 5.0    | 6.6  | MHz  | PCLK                |

| VSYNC Frequency           | Note | fVSYNC | 54  | 60     | 66   | Hz   | VSYNC               |

| VSYNC Cycle               |      | tv     | 325 | 330    | 350  | Н    | VSYNC,HSYNC         |

| VSYNC Pulse Width         |      | tw4H   | 1   | 2      |      | Н    |                     |

| Vertical Back Porch       |      | tvb    | 2   | 4      | 27   | Н    | VSYNC,HSYNC,DE      |

| Vertical Front Porch      |      | t∨f    | 2   | 4      | 27   | Н    | DB[17:0]            |

| Vertical Display Period   |      | tvdp   |     | 320    |      | Н    |                     |

| HSYNC frequency           |      | fHSYNC |     | 19.8   | 23.1 | kHz  | HSYNC               |

| HSYNC Cycle               |      | th     | 122 | 252    | 290  | CLK  | PCLK,HSYNC          |

| HSYNC Pulse Width         |      | tw5H   | 3   | 3      |      | CLK  |                     |

| Horizontal Back Porch     |      | thb    | 2   | 19     | 250  | CLK  | PCLK,HSYNC,DE       |

| Horizontal Front Porch    |      | thf    | 2   | 110    | 250  | CLK  | DB[17:0]            |

| DE Pulse Width            |      | tw6H   |     | 120    |      | CLK  | PCLK,DE             |

| Horizontal Display Period |      | thdp   |     | 120    |      | CLK  | PCLK,DE,DB[17:0]    |

Note: This is recommended spec to get high quality picture on display. It is customer's risk to use out of this frequency.

14/45) SPECIFICATIONS № 12TLM041 Issue: Jul. 13, 2012 7.5 Driving Timing Chart Case: Interface signal polarity setting Register (R0Fh): VSPL= 0, HSPL= 0, EPL= 0 and DPL= 0. -Vertical Timing t٧ tw4H VSYNC HSYNC tvdp tvb tvf DE Y320 73 DB[17:0] -Horizontal Timing tw5H HSYNC рськ ПЛАППДПЛАППАПП tw6H thb thf DE thdp thf DB[17:0]

(10/45)

#### SPECIFICATIONS № 12TLM041

Issue: Jul. 13, 2012

#### 9. Interface

#### 9.1 RGB Interface

There are two transferring mode in RGB-I/F with the RIM[1:0] setting.

The connection method to input display data is shown below, in RGB-I/F mode.

18-bit RGB interface

|       |  | (R 0Ch RIM[1:0] = 00) |                              |  |  |  |  |

|-------|--|-----------------------|------------------------------|--|--|--|--|

|       |  |                       |                              |  |  |  |  |

| DB 17 |  | R 5                   | Display data (R) input : MSB |  |  |  |  |

| DB 16 |  | R 4                   | Display data (R) input       |  |  |  |  |

| DB 15 |  | R 3                   | Display data (R) input       |  |  |  |  |

| DB 14 |  | R 2                   | Display data (R) input       |  |  |  |  |

| DB 13 |  | R 1                   | Display data (R) input       |  |  |  |  |

| DB 12 |  | R 0                   | Display data (R) input : LSB |  |  |  |  |

| DB 11 |  | G 5                   | Display data (G) input : MSB |  |  |  |  |

| DB 10 |  | G 4                   | Display data (G) input       |  |  |  |  |

| DB 9  |  | G 3                   | Display data (G) input       |  |  |  |  |

| DB 8  |  | G 2                   | Display data (G) input       |  |  |  |  |

| DB 7  |  | G 1                   | Display data (G) input       |  |  |  |  |

| DB 6  |  | G 0                   | Display data (G) input : LSB |  |  |  |  |

| DB 5  |  | B 5                   | Display data (B) input : MSB |  |  |  |  |

| DB 4  |  | B 4                   | Display data (B) input       |  |  |  |  |

| DB 3  |  | B 3                   | Display data (B) input       |  |  |  |  |

| DB 2  |  | B 2                   | Display data (B) input       |  |  |  |  |

| DB 1  |  | B 1                   | Display data (B) input       |  |  |  |  |

| DB 0  |  | B 0                   | Display data (B) input : LSB |  |  |  |  |

| ( R | (R 0Ch RIM[1:0] = 01)        |  |  |  |  |  |  |

|-----|------------------------------|--|--|--|--|--|--|

|     |                              |  |  |  |  |  |  |

| R 4 | Display data (R) input : MSB |  |  |  |  |  |  |

| R 3 | Display data (R) input       |  |  |  |  |  |  |

| R 2 | Display data (R) input       |  |  |  |  |  |  |

| R 1 | Display data (R) input       |  |  |  |  |  |  |

| R 0 | Display data (R) input : LSB |  |  |  |  |  |  |

| *   |                              |  |  |  |  |  |  |

| G 5 | Display data (G) input : MSB |  |  |  |  |  |  |

| G 4 | Display data (G) input       |  |  |  |  |  |  |

| G 3 | Display data (G) input       |  |  |  |  |  |  |

| G 2 | Display data (G) input       |  |  |  |  |  |  |

| G 1 | Display data (G) input       |  |  |  |  |  |  |

| G 0 | Display data (G) input : LSB |  |  |  |  |  |  |

| B 4 | Display data (B) input : MSB |  |  |  |  |  |  |

| B 3 | Display data (B) input       |  |  |  |  |  |  |

| B 2 | Display data (B) input       |  |  |  |  |  |  |

| B 1 | Display data (B) input       |  |  |  |  |  |  |

| B 0 | Display data (B) input : LSB |  |  |  |  |  |  |

| *   |                              |  |  |  |  |  |  |

16-bit RGB interface

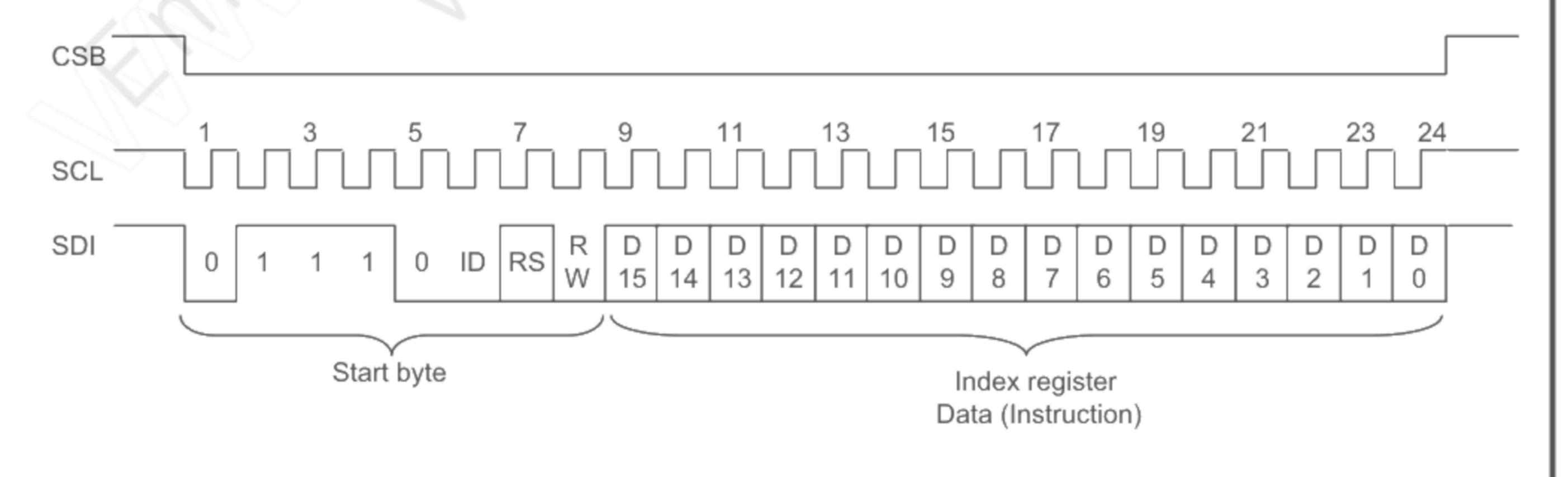

# 9.2 Serial Interface

Serial communication control block consists of the chip select pin (CSB),

the serial transfer clock pin (SCL) and the serial data input pin (SDI).

The serial communication begin the transfer on the falling edge of CSB and ends of data transfer on the rising edge of CSB.

When the initial 6bit (Start byte) is 011100, the following 16bit data is received by LSI.

The seventh data (RS bit) indicates whether the following 16bit data is "Index register" or "Data (Instruction)".

When RS=0, the following 16bit data is "Index register".

When RS=1, the following 16bit data is "Data".

# 9.2.1 Data format of serial communication (SPI)

<sup>\*</sup> If not use, connect it to GND.

17/40) SPECIFICATIONS № 12TLM041 Issue: Jul. 13, 2012 9.2.2 Register transmission The configuration of register transmission is shown below. EX: R10h = 0x1390hCSB SCL RS SDI Index register: R10h Start byte CSB SCL RS SDI Data: 1390h Start byte 9.2.3 Display data transmission The configuration of 65,536 colors display data transmission in SPI mode is shown below. Firstly, set RM=0 to start accessing GRAM via SPI. In SPI mode, 65,536 colors display data is only transferred. CSB SCL SDI Index register: R22h Start byte CSB SCL Display data 1 Display data 2 Display data 3 Start byte ORTUS TECHNOLOGY CO.,LTD.

(18/45)

Issue: Jul. 13, 2012

# SPECIFICATIONS № 12TLM041

Driving description

10.1 Register list

| ( | 1 | / | 4  | ) |

|---|---|---|----|---|

| Ι | I | E | 30 | ) |

| Index  | Command                     | IB15                                                                                                                                                                              | IB14     | IB13     | IB12        | IB11       | [IB10      | IB9     | IB8     | IB7       | IB6      | IB5     | IB4       | IB3      | IB2     | IB1      | IBO    |

|--------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------------|------------|------------|---------|---------|-----------|----------|---------|-----------|----------|---------|----------|--------|

|        | Index Register (IR)         | 0                                                                                                                                                                                 | 0        | 0        | 0           | 0          | 0          | 0       | 0       | ID7       | ID6      | ID5     | ID4       | ID3      | ID2     | ID1      | ID(    |

|        |                             |                                                                                                                                                                                   |          |          |             |            | I 0        | 4       |         | _         | _        |         |           | _        | 4       |          |        |

| DOOR   | Davisa Cada Baad            | Tho d                                                                                                                                                                             | 0        | 0        | 1           | 1 10 110 0 | 0          | 1       | 1       | 0         | 0        | 1       | 1         | 0        | 1       | 0        | 1      |

| R00h   | Device Code Read            | The d                                                                                                                                                                             | evice (  | code "   | 9335h       | is rea     | ıd out v   | vnen r  | ead th  | is regis  | iter.    |         |           |          |         |          |        |

|        |                             |                                                                                                                                                                                   | 0        | <u> </u> | ΓΛ          | Ι ο        | CM         | Λ       | 00      | 0         | Λ        |         | <u></u> Λ | Δ.       | 0       | n        | ΙΛ     |

| R01h   | Driver Output Control       | SM: S                                                                                                                                                                             | ots the  | o data   | drivor      | nin ar     | SM         | ont     | SS      | 0         | U        | 0       | 0         | U        | U       | 0        | 0      |

| 10111  | Dilver Output Control       |                                                                                                                                                                                   |          | _        |             |            | output     |         | the sc  | urce d    | river (  | 0. 51   | to \$72   | 0)       |         |          |        |

|        |                             | 00.0                                                                                                                                                                              | 0        | 0        | n           | n          | 0          | B/C     |         | 0         | 0        | 0.01    | 0 072     | 0        | 0       | 0        | Ιο     |

| R02h   | LCD Driving Control         | B/C: S                                                                                                                                                                            | Sets In  | versio   | n type.     | (1: Lir    | -          |         |         |           |          |         | Ť         | -        | Ť       |          |        |

|        |                             |                                                                                                                                                                                   | 7010 111 |          |             | (          |            | ,       |         |           |          |         |           |          |         |          |        |

|        |                             | TRI                                                                                                                                                                               | DFM      | 0        | BGR         | 0          | 0          | 0 1     | 0       | ORG       | 0        | I/D1    | I/D0      | AM       | 0       | 0        | 0      |

| R03h   | Entry Mode                  | TRI/D                                                                                                                                                                             | FM: S    | ets da   | ta tran     | sferrin    | g meth     | od to ( | GRAM    | ORG:      | Set th   | e origi | n addr    | ess of   | windo   | w area   | 1.     |

|        |                             | TRI/DFM: Sets data transferring method to GRAM. ORG: Set the origin address of window area.  BGR: Swap the R and B order of written data.  ID/AM: Control the GRAM update method. |          |          |             |            |            |         |         |           |          |         |           |          |         |          |        |

|        |                             | 0                                                                                                                                                                                 | 0        | 0        | 0           | 0          | 0          | 0       | 0       | 0         | 0        | 0       | 0         | 0        | 0       | EPF      | [1:0   |

| R05h   | 16 bits data format control | EPF:                                                                                                                                                                              | Sets R   | /B dat   | a form      | at in 1    | 6-bit m    | ode.    |         |           |          |         |           |          |         |          |        |

|        |                             |                                                                                                                                                                                   |          |          |             |            |            |         |         |           |          |         |           |          |         |          |        |

|        |                             | 0                                                                                                                                                                                 | 0        | PTD      | E[1:0]      | 0          | 0          | 0       | BASEE   | 0         | 0        | GON     | DTE       | CL       | 0       | D1       | DO     |

| R07h   | Display Control 1           | PTDE                                                                                                                                                                              | : Parti  | al ima   | ge ena      | ble bit    | s.         | V/C     | 3       | GON/      | DTE: \$  | Sets th | e outp    | ut leve  | of Ga   | ate driv | /er.   |

|        |                             | BASE                                                                                                                                                                              | E: Bas   | se ima   | ge disp     | olay er    | nable b    | it. CL: | Selec   | t 8 cold  | or mod   | e. D:0  | Control   | Sourc    | e/VCC   | )M out   | put.   |

|        |                             |                                                                                                                                                                                   |          |          | ĒΡ          | [7:0]      |            |         |         |           | 0.       |         | BP        | 7:0]     |         |          |        |

| R08h   | R08h Display Control 2      | FP: S                                                                                                                                                                             | pecify   | the lin  | e num       | ber of     | front po   | orch pe | eriod.  | 6         |          |         |           |          |         |          |        |

|        |                             | BP: S                                                                                                                                                                             | pecify   | the lin  | e num       | ber of     | back p     | orch p  | eriod.  |           | )        |         |           |          |         |          |        |

|        |                             | 0                                                                                                                                                                                 | 0        | 0        | 0           | 0          | 0          | PTS     | [1:0]   | 0         | 0        | PTG     | [1:0]     |          | ISC     | [3:0]    |        |

| R09h   | h Display Control 3         | PTS:                                                                                                                                                                              | Set the  | source   | ce outp     | out leve   | el in no   | n-disp  | lay are | ea.       |          |         |           |          |         |          |        |

|        |                             | ISC: S                                                                                                                                                                            | Set cyc  | le of g  | ate dri     | iver in    | non-dis    | splay a | area.   | PTG:      | Set the  | e scan  | mode      | in non   | -displa | ay area  | a.     |

|        |                             | 0                                                                                                                                                                                 | 0        | - 0      | 0           | 0          | 0          | 0       | 0       | 0         | 0        | 0       | 0         | FMARK    | F       | MI[2:    | 0]     |

| R0Ah   | Display Control 4           | FMAF                                                                                                                                                                              | K: FM    | ARK s    | signal o    | output     | enable     | bit in  | paralle | el interf | ace.     |         |           |          |         |          |        |

|        |                             | FMI: S                                                                                                                                                                            | Set the  | outpu    | it inter    | val of F   | MARK       | signa   | ıl.     |           |          |         |           |          |         |          |        |

|        | RGB Display Interface       | 0                                                                                                                                                                                 | O E      | NC[2:    | :0]         | 0          | 0          | 0       | RM      | 0         | 0        | DM      | [1:0]     | 0        | 0       | RIM      | 1[1:0] |

| R0Ch   | Control 1                   | ENC:                                                                                                                                                                              | Set the  | e GRA    | M writ      | e cycle    | e in RG    | B-I/F.  |         | DM: S     | Select i | nterna  | l clock   | mode     | and R   | GB-I/F   | mo     |

|        |                             | RM: S                                                                                                                                                                             | elect t  | he inte  | erface      | to acc     | ess the    | GRAI    | М.      | RIM: S    | Select   | the R   | GB-IF     | data wi  | dth.    |          |        |

|        |                             | 0                                                                                                                                                                                 | 0        | 0        | 0           | 0          | 0          | 0       |         |           |          | F       | MP[8:     | 0]       |         |          |        |

| R0Dh   | FMARK Control               | FMP:                                                                                                                                                                              | Sets th  | ne out   | put pos     | sition o   | of frame   | e cycle | (FMA    | RK) .     |          |         |           |          |         |          |        |

|        |                             |                                                                                                                                                                                   | $\sim$   |          |             |            |            | _       |         |           | _        |         |           |          | _       |          |        |

| DOE:   | RGB Display Interface       | 0                                                                                                                                                                                 | 0        | 0        | 0           | 0          | 0          | 0       | 0       | 0         | 0        | 0       |           | HSPL     |         | EPL      | DP     |

| R0Fh   | Control 2                   | VSPL                                                                                                                                                                              |          |          |             |            |            |         |         |           |          | _       |           | rity of  |         |          |        |

|        |                             | HSPL                                                                                                                                                                              | : Sets   |          | <del></del> |            |            |         |         |           |          |         |           | arity of | PCLK.   |          | Low    |

| DAOL   | Daniel Control 4            | 0                                                                                                                                                                                 | 0        | 0        | SAP         |            | _          | 3T[2:0  | )]      | APE       |          | AP[2:0  |           | 0        | 0       | SLP      |        |

| R10h   | Power Control 1             |                                                                                                                                                                                   |          |          |             |            | ble bit.   |         |         |           |          |         |           | nable /  | -       |          | _      |

| $\sim$ |                             | BT: S                                                                                                                                                                             | elect tr | ne ster  | o-up fa     | ctor of    | _          |         | 01      |           |          |         |           | de / sta |         |          |        |

| DAAL   | Daniel Ocates I O           | 0                                                                                                                                                                                 | 0        | 0        | 0           | 0          | _          | C1[2:   |         | 0         |          | C0[2:   | 0]        | 0        | \       | /C[2:0   | IJ     |

| R11h   | Power Control 2             | DC1/0                                                                                                                                                                             |          |          | -           | _          |            |         | -       | -         |          | \/0     | 14        |          |         |          |        |

|        |                             | VC: S                                                                                                                                                                             | ets the  | ratio    | Tactor      | or vCi     | to gen     | erate t |         |           |          | jes vu  | 11.       |          | VDL     | 10.01    |        |

| D12h   | Dower Control 2             | VCIDI                                                                                                                                                                             | U Colo   | 0 0      | 0           | 0          | 0          | U       |         | VCIRE     |          | 0       | 10        |          | VKF     | 1[3:0]   |        |

| R12h   | Power Control 3             | VCIR                                                                                                                                                                              |          |          |             |            |            | _       |         | ternal r  | eteren   | ice vol | tage.     |          |         |          |        |

| I      |                             | VKH:                                                                                                                                                                              | set the  | e sour   | ce out      | put VR     | EG10       | U I IeV | eı.     |           |          |         |           |          |         |          | T .    |

|        |                             | ^                                                                                                                                                                                 | _        | _ ^      |             |            | /DV /F 4 - | Ω1      |         | _ ^       | _^       |         | _ ^       | _ ^      | _ ^     |          |        |

| R13h   | Power Control 4             | 0<br>VDV:                                                                                                                                                                         | 0        | 0        | 1:41        |            | /DV[4:     |         |         | 0         | 0        | 0       | 0         | 0        | 0       | 0        | 0      |

(19/45)

Issue: Jul. 13, 2012

2/4 | IB15 | IB14 | IB13 | IB12 | IB11 | IB10 | IB9 Command IB8 IB6 | IB5 IB0 Index IB7 IB4 | IB3 IB2 IB1 AD[7:0] GRAM Horizontal Address Set AD[7:0]: Set horizontal address of GRAM. R20h AD[16:8] GRAM Vertical Address Set AD[16:8]: Set vertical address of GRAM. R21h Write (Read ) Data to GRAM R22h Write Data to GRAM VCM[5:0] R29h Power Control 5 VCM: Set the internal Vcom-DC level if OTP doesn't use. FRS[3:0] R2Bh Frame Rate Control FRS: Set the Frame rate for internal CLK circuit. KP1[2:0] KP0[2:0] R30h Gamma Control 1 KP0: Gamma-fine 0 adjustment register for positive polarity. KP1: Gamma-fine 1 adjustment register for positive polarity. KP2[2:0] KP3[2:0] R31h Gamma Control 2 KP2: Gamma-fine 2 adjustment register for positive polarity. KP3: Gamma-fine 3 adjustment register for positive polarity. KP4[2:0] KP5[2:0] R32h Gamma Control 3 KP4: Gamma-fine 4 adjustment register for positive polarity. KP5: Gamma-fine 5 adjustment register for positive polarity. RP0[2:0] RP1[2:0] R35h Gamma Control 4 RP0: Gamma-gradient 0 adjustment register for positive polarity. RP1: Gamma-gradient 1 adjustment register for positive polarity. VRP0[3:0] VRP1[4:0] R36h VRP0: Gamma-amplitude 0 adjustment register for positive polarity. Gamma Control 5 VRP1: Gamma-amplitude 1 adjustment register for positive polarity. KN1[2:0] KN0[2:0] R37h Gamma Control 6 KN0: Gamma-fine 0 adjustment register for negative polarity. KN1: Gamma-fine 1 adjustment register for negative polarity. KN2[2:0] KN3[2:0] Gamma Control 7 R38h KN2: Gamma-fine 2 adjustment register for negative polarity. KN3: Gamma-fine 3 adjustment register for negative polarity. KN4[2:0] KN5[2:0] R39h Gamma Control 8 KN4: Gamma-fine 4 adjustment register for negative polarity. KN5: Gamma-fine 5 adjustment register for negative polarity. RN0[2:0] RN1[2:0] R3Ch Gamma Control 9 RN0: Gamma-gradient 0 adjustment register for negative polarity. RN1: Gamma-gradient 1 adjustment register for negative polarity. VRN0[3:0] VRN1[4:0] R3Dh Gamma Control 10 VRN0: Gamma-amplitude 0 adjustment register for negative polarity. VRN1: Gamma-amplitude 1 adjustment register for negative polarity.

SPECIFICATIONS № 12TLM041

(20/45)

Issue: Jul. 13, 2012 SPECIFICATIONS № 12TLM041 3/4 | IB15 | IB14 | IB13 | IB12 | IB11 | IB10 | IB9 | IB7 | IB6 | IB5 | IB0 Index Command IB8 IB4 | IB3 | IB2 | IB1 HSA[7:0] R50h Horizontal Window Start Address HAS: Specify the horizontal address at the start of window area. HEA[7:0] Horizontal Window End Address HEA: Specify the horizontal address at the end of window area. R51h VSA[8:0] Vertical Window Start Address VSA: Specify the vertical address at the start of window area. R52h VEA[8:0] Vertical Window End Address VEA: Specify the vertical address at the end of window area. R53h SCN[5:0] GS 0 NL[5:0] Display Control 5 R60h GS: Sets the direction of gate scanning. SCN: Specify the start position of gate scanning. NL: Sets the number of lines to drive. Display Control 6 R61h NDL: Sets the source driver output level in the non-display area. REV: Enables the grayscale inversion. VLE: Vertical scroll display enable bit. VL[8:0] VL: Sets the scrolling amount of base image. R6Ah Display Control 7 PTDP0[8:0] Partial Image 1 Display R80h PTDP0: Sets the display start position of partial image 1. Position PTSA0[8:0] Partial image 1 RAM Start R81h PTSA0: Sets the start line address of GRAM area storing the data of partial image 1. Address PTEA0[8:0] Partial image 1 RAM End R82h PTEA0: Sets the end line address of GRAM area storing the data of partial image 1. Address PTDP1[8:0] Partial Image 2 Display R83h PTDP1: Sets the display start position of partial image 2. Position PTSA1[8:0] Partial image 2 RAM Start

R84h

R85h

Address

Partial image 2 RAM End

Address

PTSA1: Sets the start line address of GRAM area storing the data of partial image 2.

PTEA1: Sets the end line address of GRAM area storing the data of partial image 2.

PTEA1[8:0]

(21/45)

Issue: Jul. 13, 2012

4/4 | IB15 | IB14 | IB13 | IB12 | IB11 | IB10 | IB9 | IB6 IB2 IB0 Index Command IB8 IB7 IB5 IB4 | IB3 | IB1 DIVI[1:0] RTNI[4:0] R90h Panel Interface Control 1 RTNI: Sets 1H (line) clock number in internal clock mode. DIVI: Sets the division ratio in internal clock mode. NOWI[2:0] R92h Panel Interface Control 2 NOWI: Sets the gate output non-overlap period in internal clock mode. DIVE[1:0] Panel Interface Control 3 R95h DIVE: Sets the division ratio of PCLK in RGB-I/F mode. NOWE[3:0] R97h Panel Interface Control 4 NOWE: Sets the gate output non-overlap period in RGB-I/F mode. VCM\_OTP[5:0] PGMEN RA1h OTP Control 1 PGMEN: OTP programming enable bit. VCM\_OTP: OTP programming data for VCOMH voltage. VCM\_D[5:0] VÇMEN PGM\_CNT[1:0] RA2h OTP Control 2 PGM\_CNT: OTP programmed record. (Read only) VCMEN: OTP VCM data enable bit. VCM\_D: OTP VCM data read value. (Read only) KEY[15:0] OTP Programming ID key protection. RA5h OTP Control 3 D\$TB Deep Standby Control RE6h DSTB: Set the deep standby mode. memw memw drv r\_gnt | r\_req | gnt req memwr\_gnt: When the LSI doesn't grant writing data to GRAM, this bit is 1. (Normal operation) TEST Register 1 RE8h (Read Only) memwr\_req: When the LSI doesn't request writing data to GRAM, this bit is 1. (Normal operation) drv\_gnt: When the LSI doesn't grant reading data from GRAM, this bit is 1. (Normal operation) dry reg: When the LSI doesn't request reading data from GRAM, this bit is 1. (Normal operation) TEST Register 2 REFh

SPECIFICATIONS № 12TLM041

(22/40)

SPECIFICATIONS № 12TLM041

Issue: Jul. 13, 2012

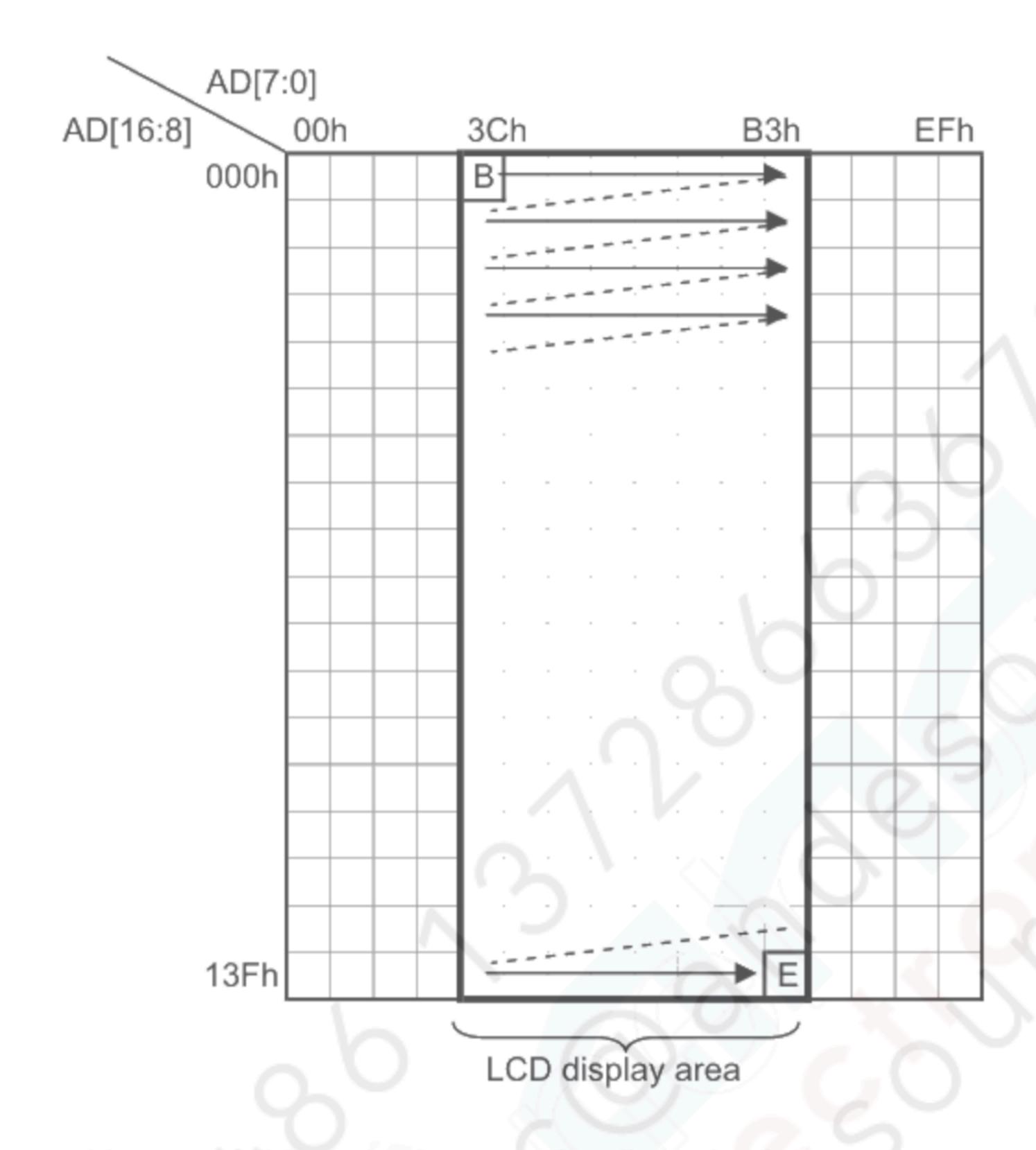

#### 10.2 GRAM Address

The LSI has 240 x 320 x 18bit GRAM, and this panel uses 120 x 320 x 18bit of them as follows. Display data is written to specified window area.

So, set address as follows when you rewrite all viewing image.

| Window address | R50h | HSA[7:0] = 8'h3C  |

|----------------|------|-------------------|

|                | R51h | HEA[7:0] = 8'hB3  |

|                | R52h | VSA[8:0] = 9'h000 |

|                | R53h | VEA[8:0] = 9'h13F |

In the case that writing direction is normal, R03h = 16'h1030h (ID[1:0] = 11, AM = 0), set the start address is as follows.

R20h AD[7:0] = 8'h3C R21h AD[16:8] = 9'h000

Please make sure to set AM = 0 (Horizontal writhing direction) in RGB-I/F mode.

(23/43) Issue: Jul. 13, 2012

# SPECIFICATIONS № 12TLM041 10.3 RGB <=> Internal Clock Operation The following sequence is the method to switch between the internal clock mode and the RGB-I/F mode. [internal clock mode -> RGB-I/F mode] Internal clock operation (DM=00/RM=0) ID[1:0] = 11, AM = 0R03h = 1030hSet address HSA[7:0]=8'h3C R50h = 003ChDisplay operation with internal clock. HEA[7:0]=8'hB3 R51h = 00B3hVSA[8:0]=9'h000 R52h = 0000hVEA[8:0]=9'h13F R53h = 013FhAD[7:0]=8'h3C R20h = 003ChAD[16:8]=9'h000 R21h = 0000hSignals for RGB-I/F input start Input PCLK/ Note: Input the signals for RGB-I/F HSYNC/VSYNC before setting DM/RM. Set RGB-I/F mode RM=1, DM[1:0]=01 R0Ch = 0111hSet index register R22h Wait 1 frame or more

# ORTUS TECHNOLOGY CO.,LTD.

(24/45)

SPECIFICATIONS № 12TLM041

Issue: Jul. 13, 2012

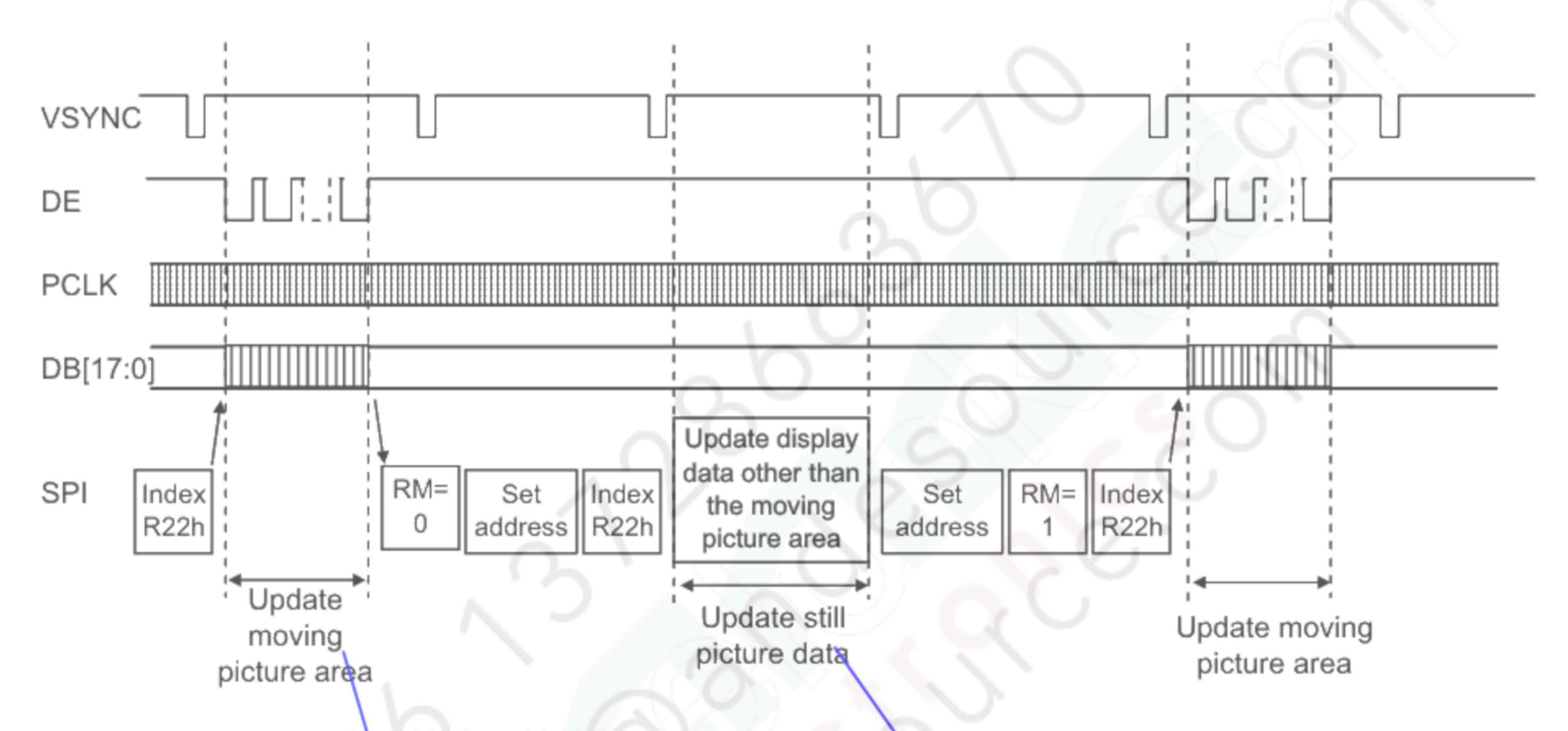

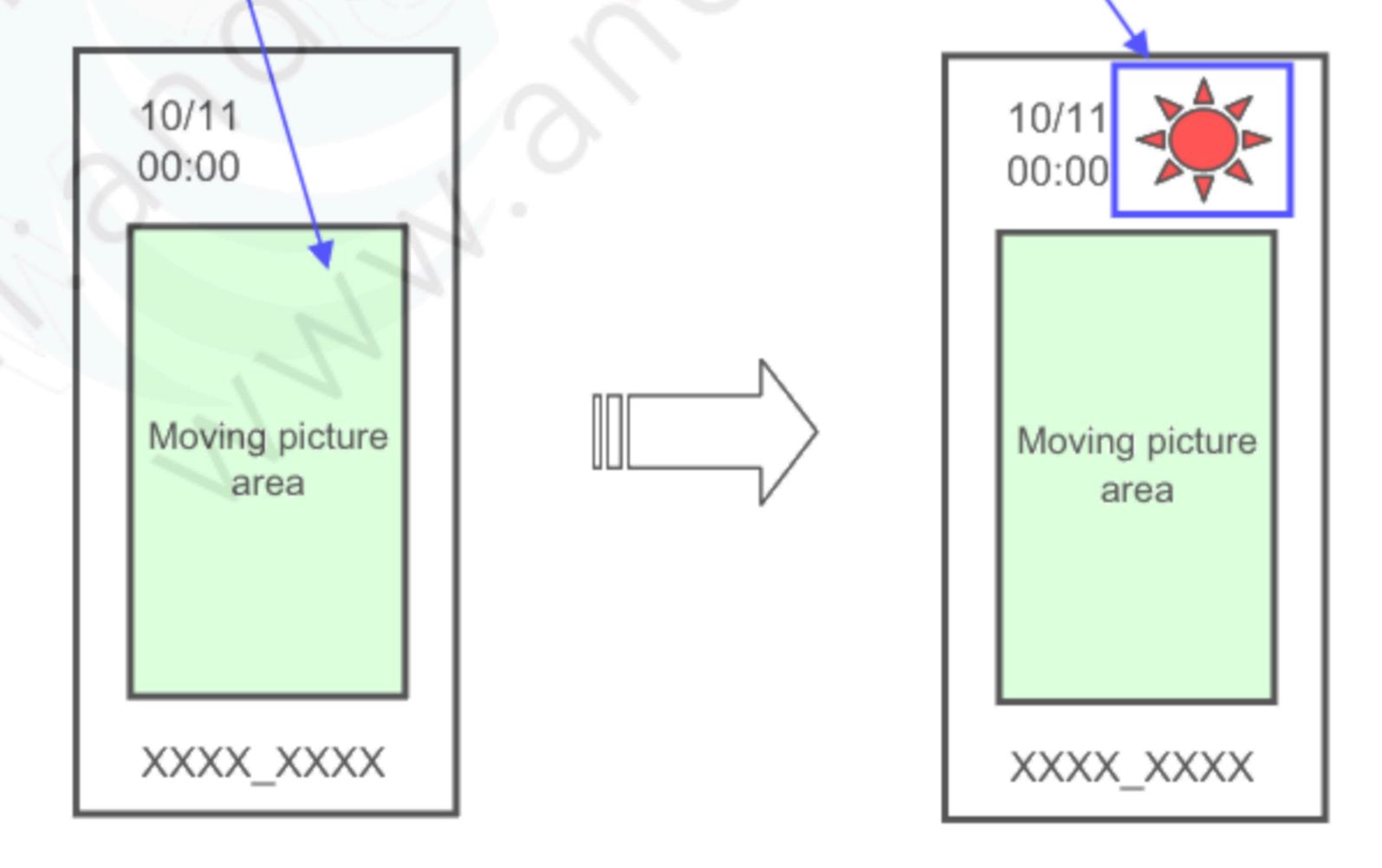

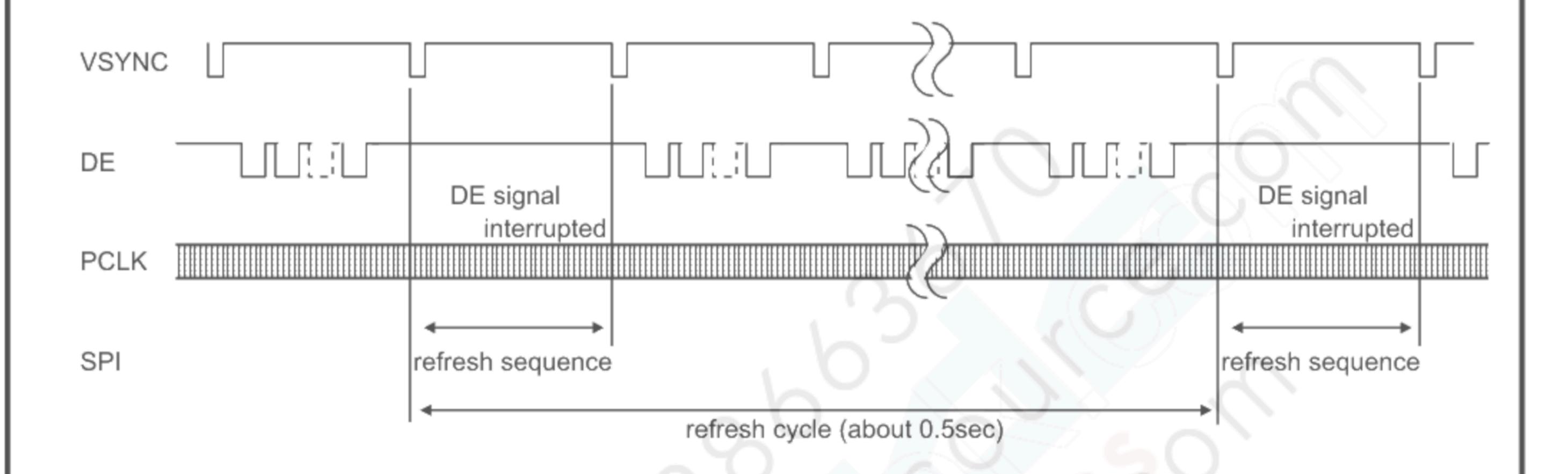

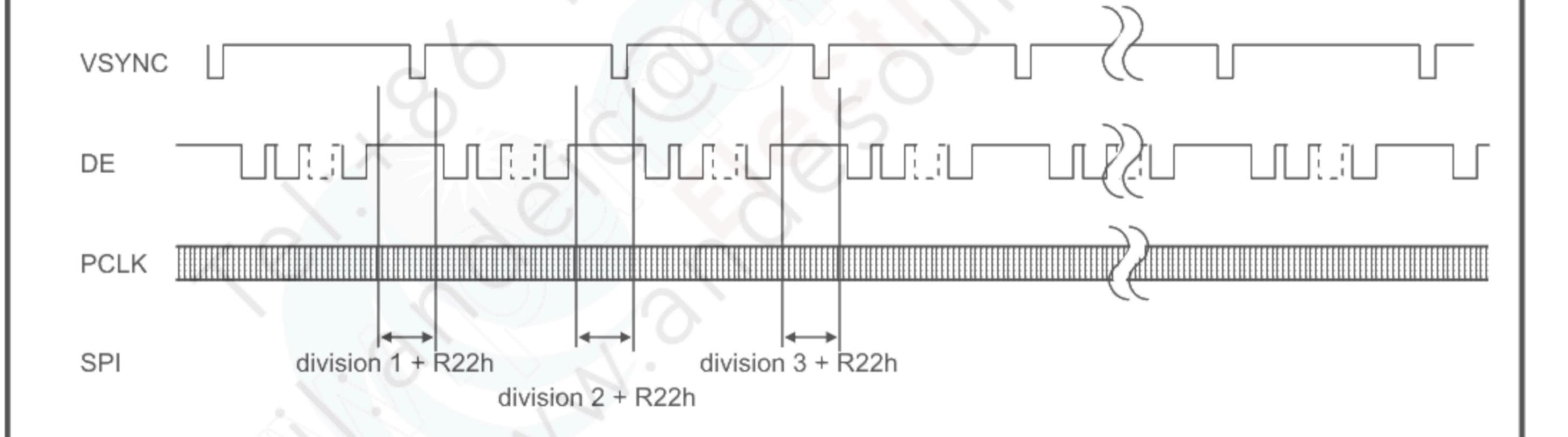

#### 10.4 Update Still Picture Area in Moving Picture Mode

The panel allows GRAM access via the system interface (SPI) in RGB-I/F mode.

In RGB-I/F mode, the data are written to GRAM in synchronization with PCLK at DE=Low (DPL=0).

So, when write data to GRAM by system interface (SPI), set DE=Hi to terminate writing data by RGB-I/F.

And, set RM=0 to access GRAM by system interface (SPI).

When restart GRAM access in RGB-I/F mode, wait read/write cycle

and then set RM=1 and the INDEX register to R22h to start accessing GRAM via RGB-I/F.

Example of update the still picture data in moving picture mode.

Note1: Input VSYNC/HSYNC/PCLK constantly in RGB-I/F mode.

Note2: The address is set every falling edge of VSYNC (VSPL=0) in RGB-I/F mode.

Note3: Set address and INDEX register (R22h) before starting GRAM access

in RGB-I/F mode.

Note4: "Set address" is consist of setting window address and writing start address.

(25/45)

# SPECIFICATIONS № 12TLM041

# Issue: Jul. 13, 2012

# Sequence

# 11.1 Power-ON Sequence

| Register Data  | Comment                         | Detail                  |

|----------------|---------------------------------|-------------------------|

| VCC_ON         | Power ON                        |                         |

| RESB = Low     | Set RESB=0                      |                         |

| Wait ≧ 1 msec  | Wait                            |                         |

| RESB = High    | Set RESB=1                      |                         |

| Wait ≥ 50 msec | Wait                            |                         |

| R07h 0000h     | Set R07h to turn off the panel. | DTE=0, D[1:0]=00, GON=0 |

LCD\_Power Supply ON sequence

| 0000h    | Initialize Power Control 1 (Stop operation)                                    | SAP=0,BT[2:0]=3'b000,APE=0,AP[2:0]=3'b000,<br>SLP=0,STB=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|----------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0007h    | Initialize Power Control 2 (Stop step-up)                                      | DC1[2:0]=3'b000,DC0[2:0] =3'b000,VC[2:0] =3'b111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 0000h    | Initialize Power Control 3 (stop regulator)                                    | VCIRE=0,VRH[3:0]=4'b0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 0000h    | Initialize Vcom amplitude                                                      | VDV[4:0]= 5'b00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

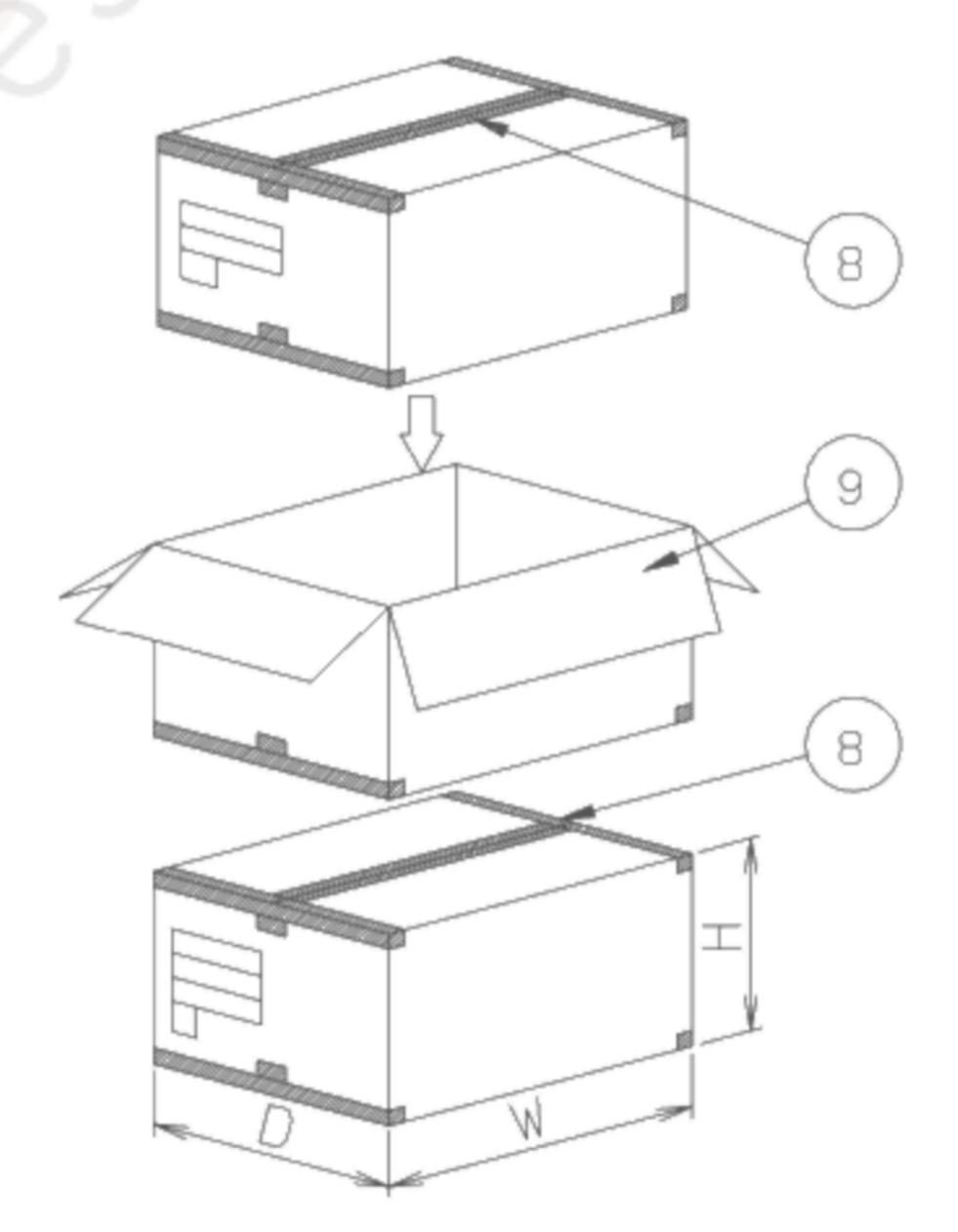

| 200 msec |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |