| MODEL N | VO. | TM035PDHG03-00 |

|---------|-----|----------------|

|         |     |                |

ISSUED DATE: 2014-09-05

VERSION: Ver 2.0

□ Preliminary Specification

■ Final Product Specification

Customer:\_\_\_

| Approved by | Notes |

|-------------|-------|

|             |       |

|             |       |

|             |       |

#### **TIANMA Confirmed:**

| Prepared by | Checked by | Approved by |

|-------------|------------|-------------|

| 刘文龙         | 梁毅华        | 谭峰          |

# **Table of Contents**

| Table of Contents                     | 2  |

|---------------------------------------|----|

| Record of Revision                    | 3  |

| 1 General Specifications              | 4  |

| 2 Input/Output Terminals              | 5  |

| 3 Absolute Maximum Ratings            | 7  |

| 4 Electrical Characteristics          | 7  |

| 5 Timing Chart                        | 9  |

| 6 Optical Characteristics             | 24 |

| 7 Environmental / Reliability Test    | 27 |

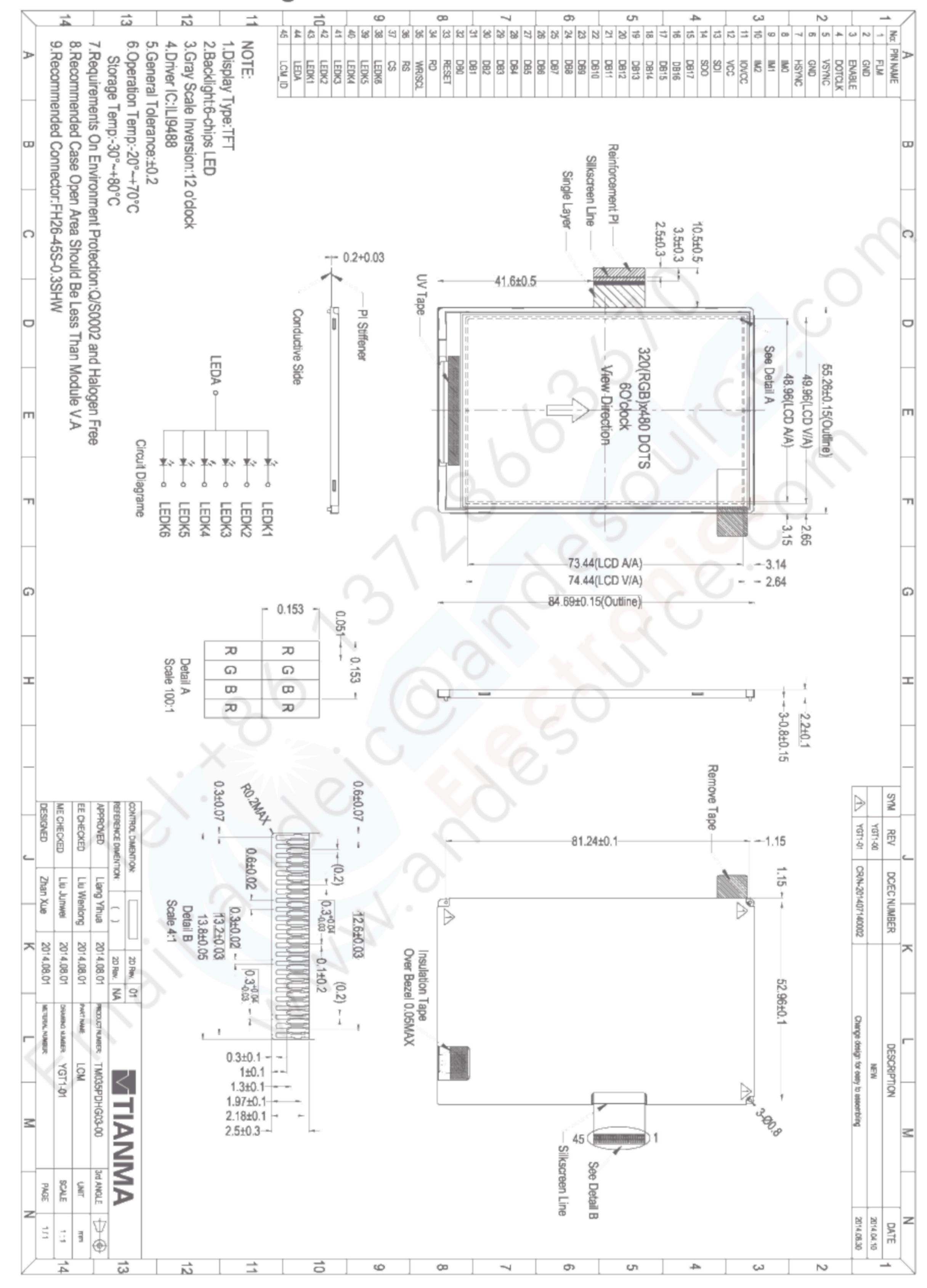

| 8 Mechanical Drawing                  | 28 |

| 9 Packing Drawing                     | 29 |

| 10 Precautions for Use of LCD Modules | 30 |

# Record of Revision

| Rev | Issued Date | Description                                                               | Editor      |

|-----|-------------|---------------------------------------------------------------------------|-------------|

| 1.0 | 2014-04-10  | Preliminary Specification Release                                         | Wenlong Liu |

| 1.1 | 1014-04-28  | Modify the mistake of RA test requirements                                | Yihua_liang |

| 2.0 | 2014-09-05  | Final Product Release. change mechanical drawing, optical characteristics | Wenlong Liu |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     | 0           |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

|     |             |                                                                           |             |

# 1 General Specifications

|                               | Feature                        | Spec                   |  |  |

|-------------------------------|--------------------------------|------------------------|--|--|

|                               | Size                           | 3.5 inch               |  |  |

|                               | Resolution                     | 320(RGB) x 480         |  |  |

|                               | Technology Type                | a-Si                   |  |  |

|                               | Pixel Configuration            | R.G.B. Vertical Stripe |  |  |

| Display Spec.                 | Pixel pitch(mm)                | 0.153(H)x0.153(V)      |  |  |

|                               | Display Mode                   | TM with Normally White |  |  |

|                               | Surface Treatment              | HC                     |  |  |

|                               | Viewing Direction              | 6 o'clock              |  |  |

|                               | Gray Scale Inversion Direction | 12 o'clock             |  |  |

|                               | LCM (W x H x D) (mm)           | 55.26 x 84.69 x 2.2    |  |  |

|                               | Active Area(mm)                | 48.96x73.44            |  |  |

| Mechanical                    | With /Without TSP              | Without TSP            |  |  |

| Characteristics               | Connection Type                | Zif                    |  |  |

|                               | LED Numbers                    | 6 LEDs                 |  |  |

|                               | Weight (g)                     | 21.0                   |  |  |

|                               | Interface                      | MCU+RGB+SPI            |  |  |

| Electrical<br>Characteristics | Color Depth                    | 65K/262K               |  |  |

| Characteristics               | Driver IC                      | ILI9488                |  |  |

Note 1: Viewing direction for best image quality is different from TFT definition. There is a 180 degree shift.

Note 2: Requirements on Environmental Protection: Q/S0002+HF

Note 3: LCM weight tolerance: ± 5%

# 2 Input/Output Terminals

| Pin<br>No. | Symbol | Symbol I/O Function |                                                                                                                                               |  |  |  |  |

|------------|--------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1          | FLM    | 0                   | Output a frame head pulse signal If no used, please open this pin                                                                             |  |  |  |  |

| 2          | GND    | Р                   | Ground                                                                                                                                        |  |  |  |  |

| 3          | ENABLE | I                   | Data enable signal in RGB mode If no used, please fix this pin at GND level                                                                   |  |  |  |  |

| 4          | DOTCLK | I                   | Pixel clock signal in RGB mode  If no used, please connect this pin to GND                                                                    |  |  |  |  |

| 5          | VSYNC  | I                   | Vertical sync. signal in RGB mode If no used, please connect this pin to GND                                                                  |  |  |  |  |

| 6          | GND    | Р                   | Ground                                                                                                                                        |  |  |  |  |

| 7          | HSYNC  | I                   | Horizontal sync, signal in RGB mode If no used, please connect this pin to GND                                                                |  |  |  |  |

| 8          | IMO    | I                   | MPU system interface mode select                                                                                                              |  |  |  |  |

| 9          | IM1    | I                   | MPU system interface mode select                                                                                                              |  |  |  |  |

| 10         | IM2    | I                   | MPU system interface mode select                                                                                                              |  |  |  |  |

| 11         | IOVCC  | р                   | IO POWER                                                                                                                                      |  |  |  |  |

| 12         | VCC    | Р                   | Analog POWER                                                                                                                                  |  |  |  |  |

| 13         | SDI    | I/O                 | Serial data in/out pin in DBI Type C 9bit mode<br>Serial data input pin in DBI Type B 8bit mode<br>If no used, please connect this pin to GND |  |  |  |  |

| 14         | SDO    | 0                   | Serial data output pin If no used, leave this pin open                                                                                        |  |  |  |  |

| 15         | DB17   | - I/O               | Data Bus                                                                                                                                      |  |  |  |  |

| 16         | DB16   | I/O                 | Data Bus                                                                                                                                      |  |  |  |  |

| 17         | DB15   | I/O                 | Data Bus                                                                                                                                      |  |  |  |  |

| 18         | DB14   | I/O                 | Data Bus                                                                                                                                      |  |  |  |  |

| 19         | DB13   | I/O                 | Data Bus                                                                                                                                      |  |  |  |  |

| 20         | DB12   | I/O                 | Data Bus                                                                                                                                      |  |  |  |  |

| 21         | DB11   | I/O                 | Data Bus                                                                                                                                      |  |  |  |  |

| 22         | DB10   | I/O                 | Data Bus                                                                                                                                      |  |  |  |  |

| 23         | DB9    | I/O                 | Data Bus                                                                                                                                      |  |  |  |  |

| 24         | DB8    | I/O                 | Data Bus                                                                                                                                      |  |  |  |  |

| 25         | DB7    | I/O                 | Data Bus                                                                                                                                      |  |  |  |  |

| 26         | DB6    | I/O                 | Data Bus                                                                                                                                      |  |  |  |  |

### Model No.TM035PDHG03-00 V2.0

|    |        |     | MOGGI HOLLINGOU DILOGO OU VIIO                                                                                                  |

|----|--------|-----|---------------------------------------------------------------------------------------------------------------------------------|

| 27 | DB5    | I/O | Data Bus                                                                                                                        |

| 28 | DB4    | I/O | Data Bus                                                                                                                        |

| 29 | DB3    | I/O | Data Bus                                                                                                                        |

| 30 | DB2    | I/O | Data Bus                                                                                                                        |

| 31 | DB1    | I/O | Data Bus                                                                                                                        |

| 32 | DB0    | I/O | Data Bus                                                                                                                        |

| 33 | RESET  | I   | Reset pin                                                                                                                       |

| 34 | RD     | I   | Read strobe signal If no used, please connect this pin to IOVCC                                                                 |

| 35 | WR/SCL | I   | (WR) Write data enable pin in DBI Type B (SCL) Write data enable pin in DBI Type C If no used, please connect this pin to IOVCC |

| 36 | RS     | I   | Data/command selection pin If no used, please connect this pin to IOVCC                                                         |

| 37 | CS     | I   | Chip select signal If no used, please connect this pin to IOVCC                                                                 |

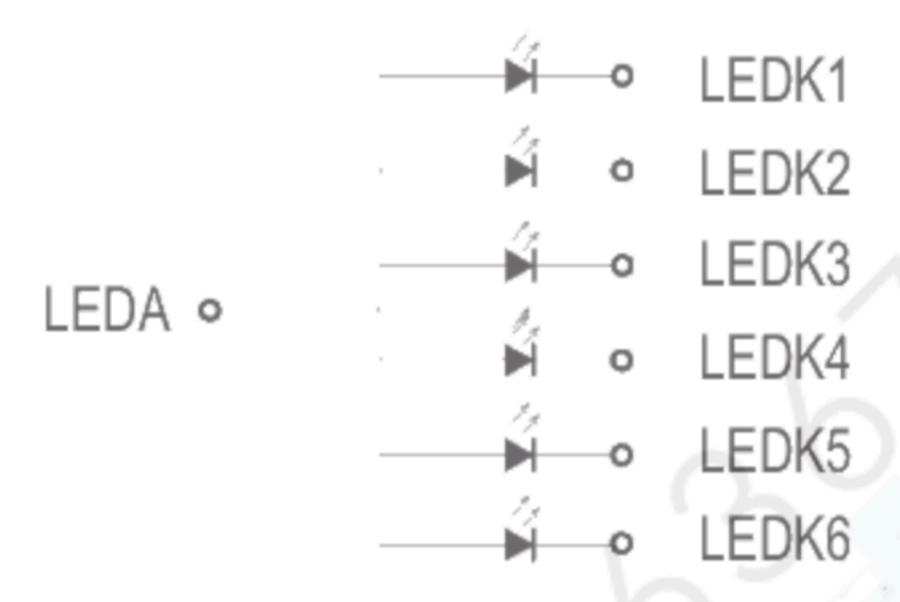

| 38 | LEDK6  | Р   | LED CATHODE                                                                                                                     |

| 39 | LEDK5  | Р   | LED CATHODE                                                                                                                     |

| 40 | LEDK4  | Р   | LED CATHODE                                                                                                                     |

| 41 | LEDK3  | Р   | LED CATHODE                                                                                                                     |

| 42 | LEDK2  | Р   | LED CATHODE                                                                                                                     |

| 43 | LEDK1  | Р   | LED CATHODE                                                                                                                     |

| 44 | LEDA   | Р   | LED ANODE                                                                                                                       |

| 45 | LCM_ID | 0   | Customer requirement: 1.8V                                                                                                      |

|    |        |     |                                                                                                                                 |

Note1: I/O definition: I----Input O---Output P----Power/ Ground NC---Not Connected

| IM2 | IM1 | IM0   | Interface                   | WR/SCL | DATA Bus use     |                 |  |

|-----|-----|-------|-----------------------------|--------|------------------|-----------------|--|

|     |     |       |                             |        | Command/Parament | GRAM            |  |

| 0   | 0   | 0     | DBITYPE-B18-bit             | WR     | DB7-DB0          | DB17-DB0:18bits |  |

|     |     | 1/3/1 | (DB_EN='0')                 |        |                  | Data            |  |

| 0   | 0   | 1     | DBI TYPE-B 9-bit            | WR     | DB7-DB0          | DB8-DB0:9bits   |  |

|     |     |       |                             |        |                  | Data            |  |

| 0   | 1   | 0     | DBI TYPE-B 16-bit           | WR     | DB7-DB0          | DB15-DB0:16bits |  |

|     |     |       |                             |        |                  | Data            |  |

| 0   | 1   | 1     | DBI TYPE-B 8-bit            | WR     | DB7-DB0          | DB7-DB0:8bits   |  |

|     |     | 1     |                             |        |                  | Data            |  |

| 1   | 0   | 1     | DBI TYPE-C Option 1(3 wire) | SCL    | SDA/SDO          |                 |  |

| 1   | 1   | 1     | DBI TYPE-C Option 3(4 wire) | SCL    | SDA/SDO          |                 |  |

Table 2.1 System interface select

# 3 Absolute Maximum Ratings

Ta=25°C

| ltem                          | Symbol                 | MIN  | MAX       | Unit | Remark       |

|-------------------------------|------------------------|------|-----------|------|--------------|

| Power Supply Voltage          | VCI                    | -0.3 | 3.3       | V    |              |

| Logic Supply Voltage          | IOVCC                  | -0.3 | 3.3       | V    |              |

| Logic Input voltage           | RESET,CSX,SCL,SDA,D/CX | -0.3 | IOVCC+0.3 | V    |              |

| Back Light Forward<br>Current | I <sub>LED</sub>       |      | 20        | mA   | For Each LED |

| Operating Temperature         | T <sub>OPR</sub>       | -20  | 70        | °C   |              |

| Storage Temperature           | T <sub>STG</sub>       | -30  | 80        | °C   |              |

Table 3.1 Absolute maximum rating

## 4 Electrical Characteristics

### 4.1 LCD module

Ta=25°C

|                      | tem                   | Symbol        | MIN       | TYP     | MAX       | Unit | Remark                 |

|----------------------|-----------------------|---------------|-----------|---------|-----------|------|------------------------|

|                      | gnal Input<br>Voltage | IOVCC         | 1.65      | 1.8     | 3.3       | V    |                        |

| Power S<br>Voltage   |                       | VCI           | 2.5       | 2.8     | 3.3       | V    |                        |

| Input<br>Signal      | High Level            | VIH           | 0.7*IOVCC |         | IOVCC     | V    | RESET,CSX,SCL,SDA,D/CX |

| -                    | Low Level             | VIL           | -0.3      | -       | 0.3*IOVCC | V    |                        |

| Output<br>Signal     | High Level            | VOH           | 0.8*IOVCC |         | IOVCC     | V    |                        |

| _ ~                  | Low Level             | VOL           | 0         | <u></u> | 0.2*IOVCC | V    |                        |

| (Panel+              | LSI)                  | Black Mode    |           | 44.1    | _         | mW   |                        |

| Power<br>Consumption |                       | Sleeping Mode | -         | 750     | _         | uW   |                        |

Table 4.1 LCD module electrical characteristics

4.2 Backlight Unit

Ta=25°C

| Item                        | Symbol          | Min | Тур | Max | Unit | Remark             |

|-----------------------------|-----------------|-----|-----|-----|------|--------------------|

| Forward Current             | I <sub>F</sub>  | _   | 20  | _   | mA   | 1 LED              |

| Forward Voltage             | V <sub>F</sub>  | _   | 3.2 | _   | V    | 1 LED              |

| Backlight Power Consumption | W <sub>BL</sub> | _   | 384 | _   | mW   | 6 LEDs in parallel |

Note1: Figure below shows the connection of backlight LED.

Note 2: 1LED:  $V_F = 3.2V$   $I_F = 20mA$ Note 3: :  $I_F$  is defined for one LED.

Optical performance should be evaluated at Ta=25°C only.

If LED is driven by high current, high ambient temperature & humidity condition. The life time of LED will be reduced. Operating life means brightness goes down to 50% initial brightness. Typical operating life time is estimated data.

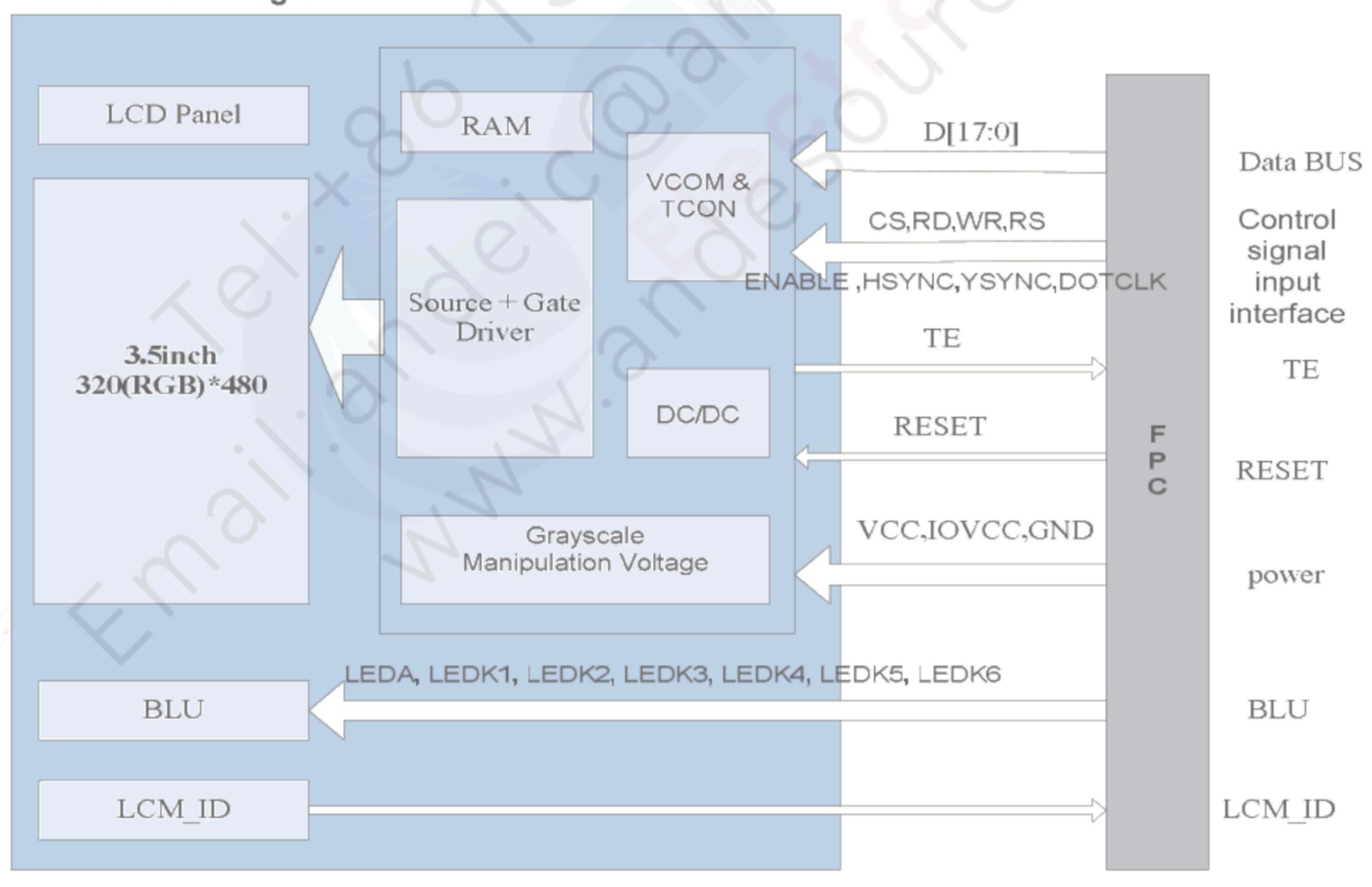

## 4.3 Block Diagram

# 5 Timing Chart

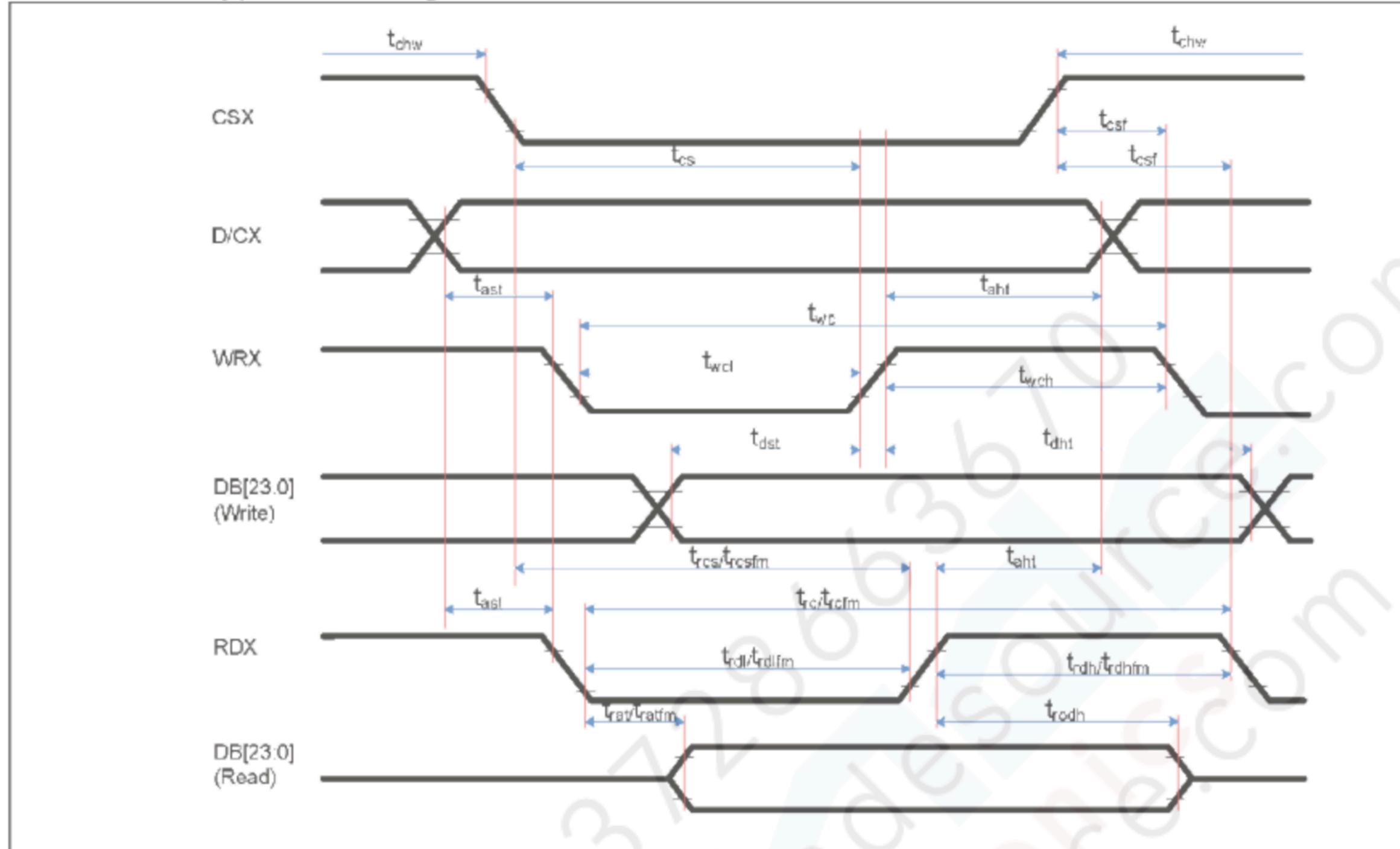

## 5.1 DBI Type B

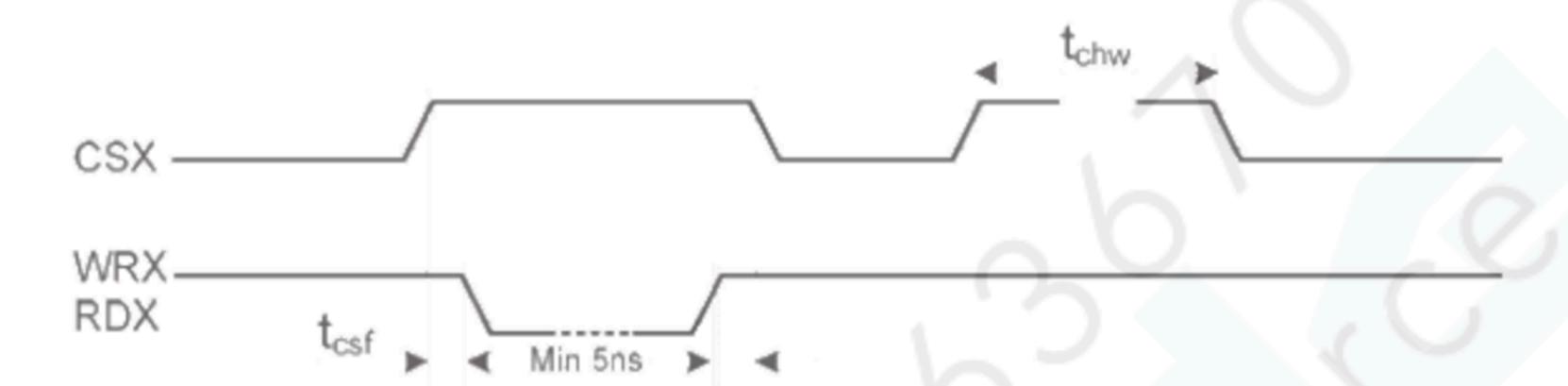

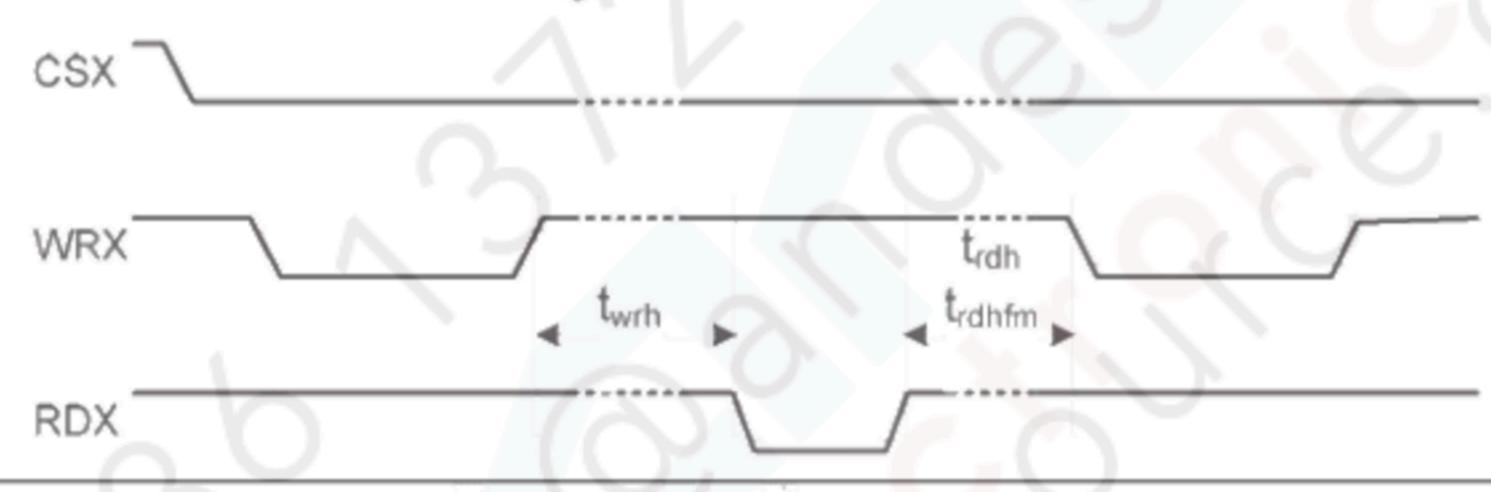

5.1.1 DBI Type B Timing Characteristic

| Signal                   | Symbol | Parameter                          | min | max      | Unit | Description                    |

|--------------------------|--------|------------------------------------|-----|----------|------|--------------------------------|

| DOV                      | tast   | Address setup time                 | 0   |          | ns   | -                              |

| DCX                      | that   | Address hold time (Write/Read)     | 0   | -        | ns   | -                              |

|                          | tchw   | CSX "H" pulse width                | 0   | <u> </u> | ns   | _                              |

|                          | 1cs    | Chip Select setup time (Write)     | 15  | -        | ns   | _                              |

| CSX                      | trcs   | Chip Select setup time (Read ID)   | 45  | ^        | ns   | -                              |

|                          | trosfm | Chip Select setup time (Read FM)   | 355 | -        | ns   | ~                              |

|                          | test   | Chip Select Wait time (Write/Read) | 0   | -        | ns   | -                              |

|                          | twc    | Write cycle                        | 40  | -        | ns   | -                              |

| WRX                      | twrh   | Write Control pulse H duration     | 15  | -        | ns   | -                              |

|                          | twrl   | Write Control pulse L duration     | 15  | -        | ns   | _                              |

|                          | trofm  | Read Cycle (FM)                    | 450 | -        | ns   |                                |

| RDX (FM)                 | trdhfm | Read Control H duration (FM)       | 90  |          | ns   | When read from Frame<br>Memory |

|                          | trdlfm | Read Control L duration (FM)       | 355 | - v      | ns   | Meniory                        |

|                          | trc    | Read cycle (ID)                    | 160 |          | ns   |                                |

| RDX (ID)                 | trdh   | Read Control pulse H duration      | 90  |          | ns   | When read ID data              |

|                          | trdl   | Read Control pulse L duration      | 45  | -        | ns   |                                |

| DB [33·0]                | tdst   | Write data setup time              | 10  | -        | ns   |                                |

| DB [23:0],<br>DB [17:0], | tdht   | Write data hold time               | 10  |          | ns   |                                |

| DB [15:0],               | trat   | Read access time                   | -   | 40       | ns   | For maximum, CL=30pF           |

| DB [8:0],                | tratfm | Read access time                   | -   | 340      | ns   | For minimum, CL=8pF            |

| DB [7:0]                 | trod   | Read output disable time           | 20  | 80       | ns   |                                |

#### Notes:

- 1. Ta = -30 to 70 °C, IOVCC = 1.65V to 3.3V, VCI = 2.5V to 3.3V, AGND = DGND = 0V

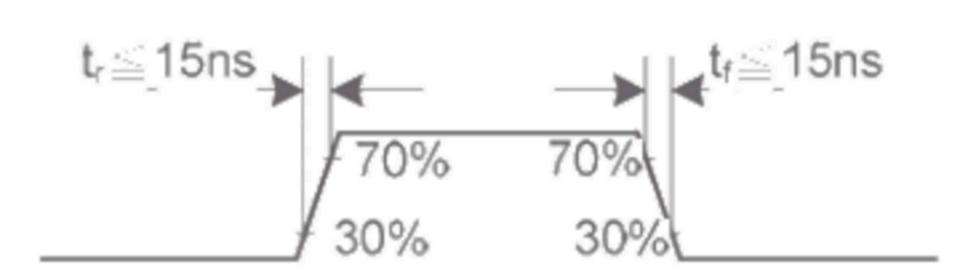

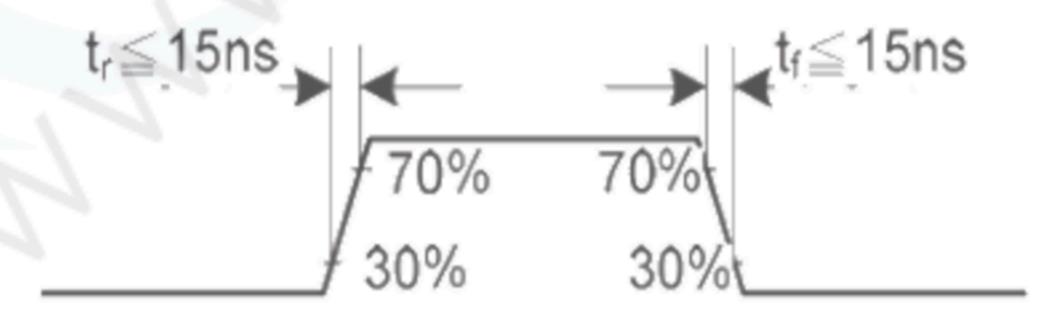

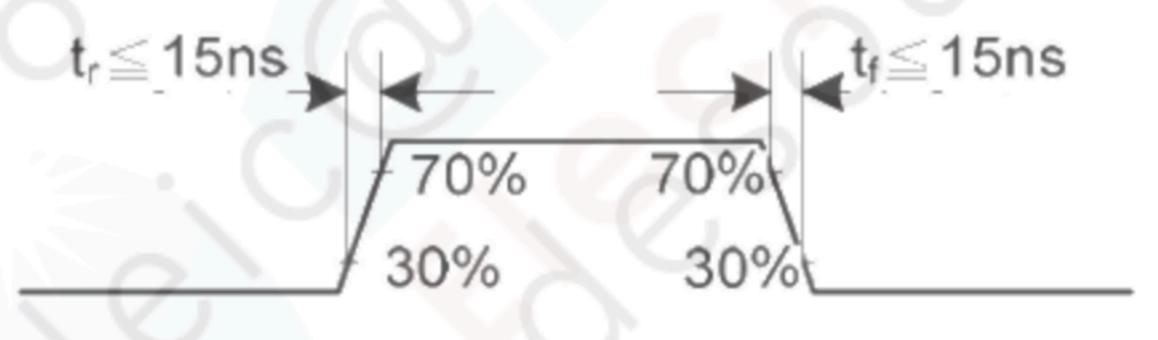

- 2. Logic high and low levels are specified as 30% and 70% of IOVCC for input signals.

- 3. Input signal rising time and falling time:

4. The CSX timing:

5. The Write to Read or the Read to Write timing:

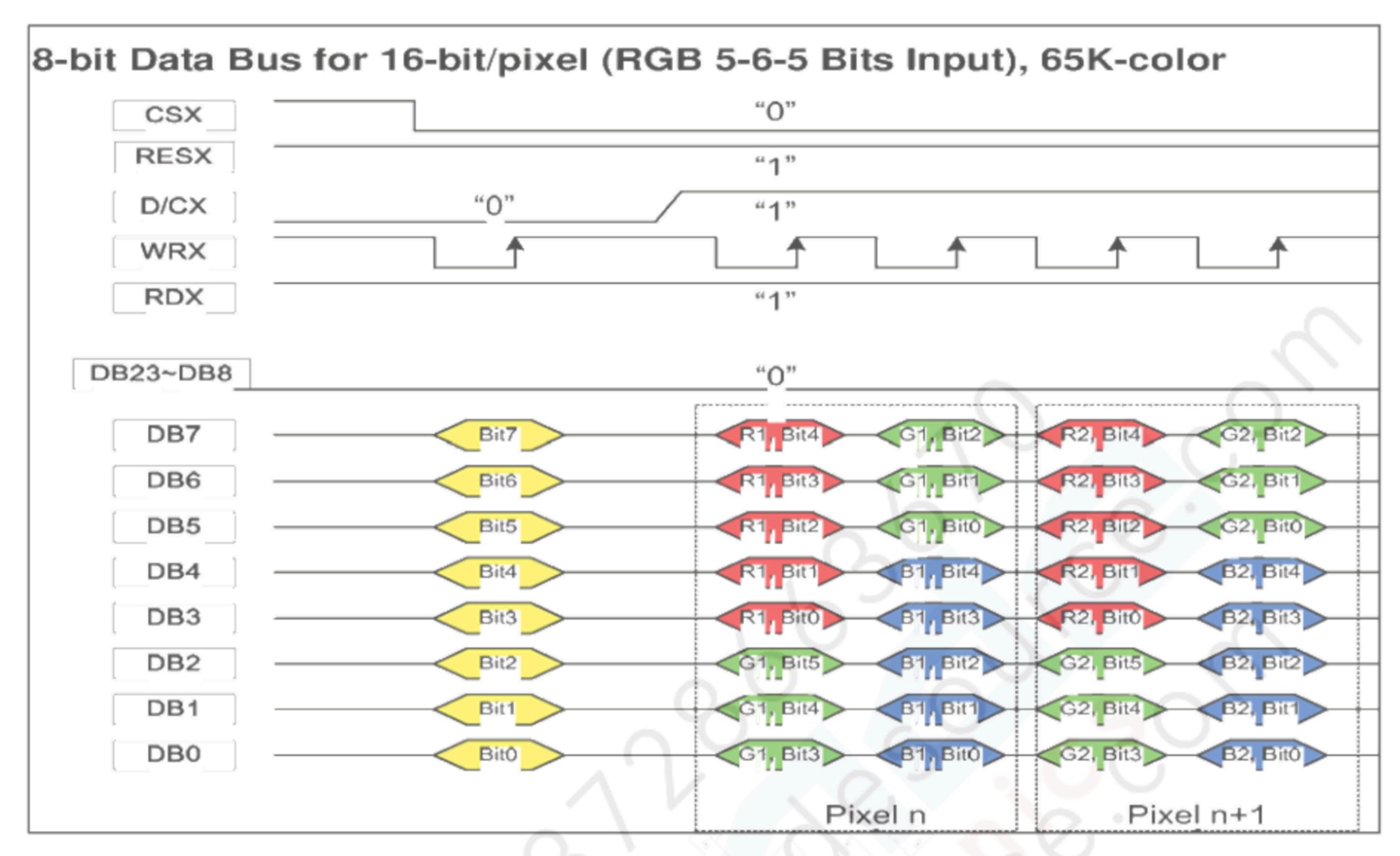

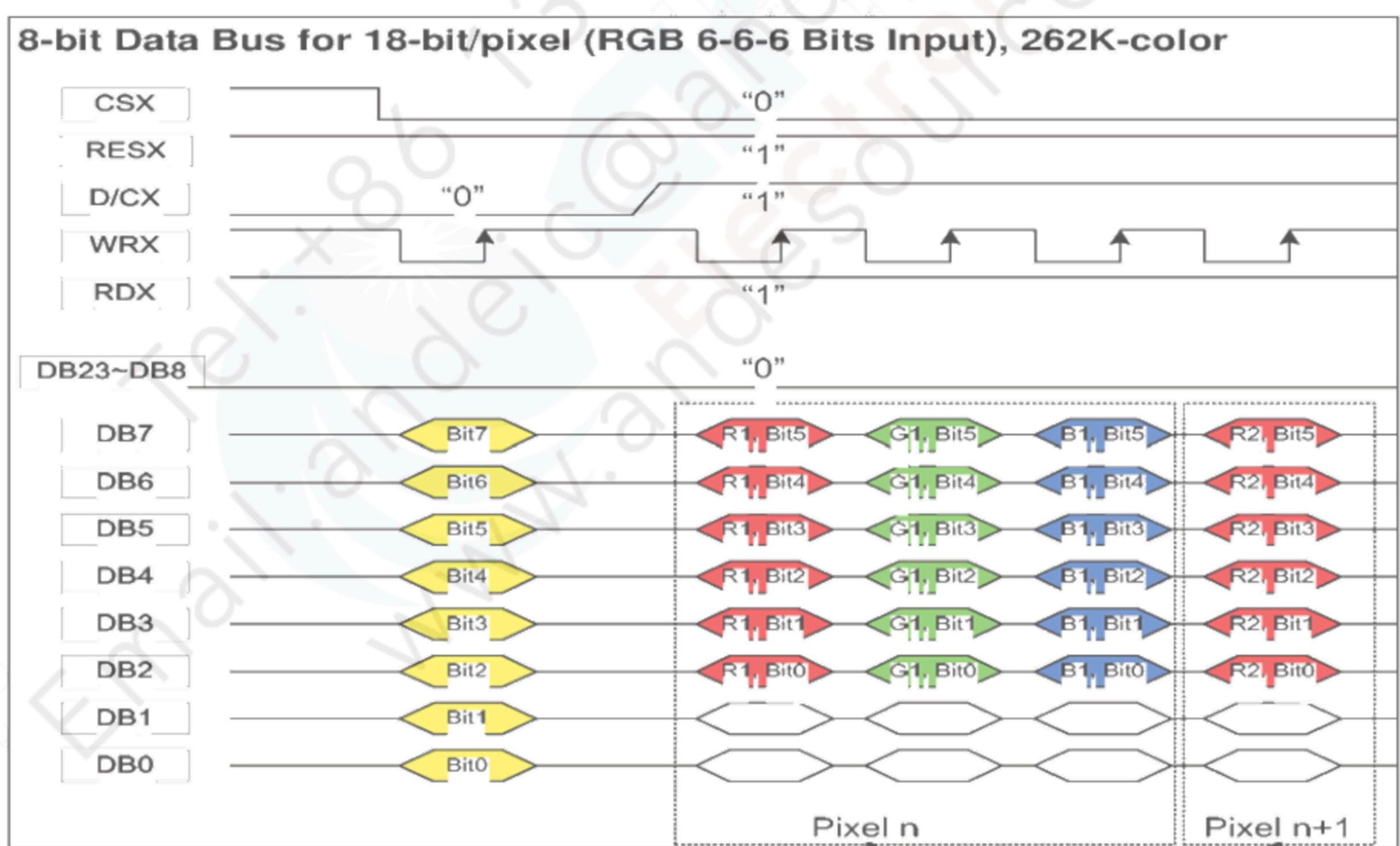

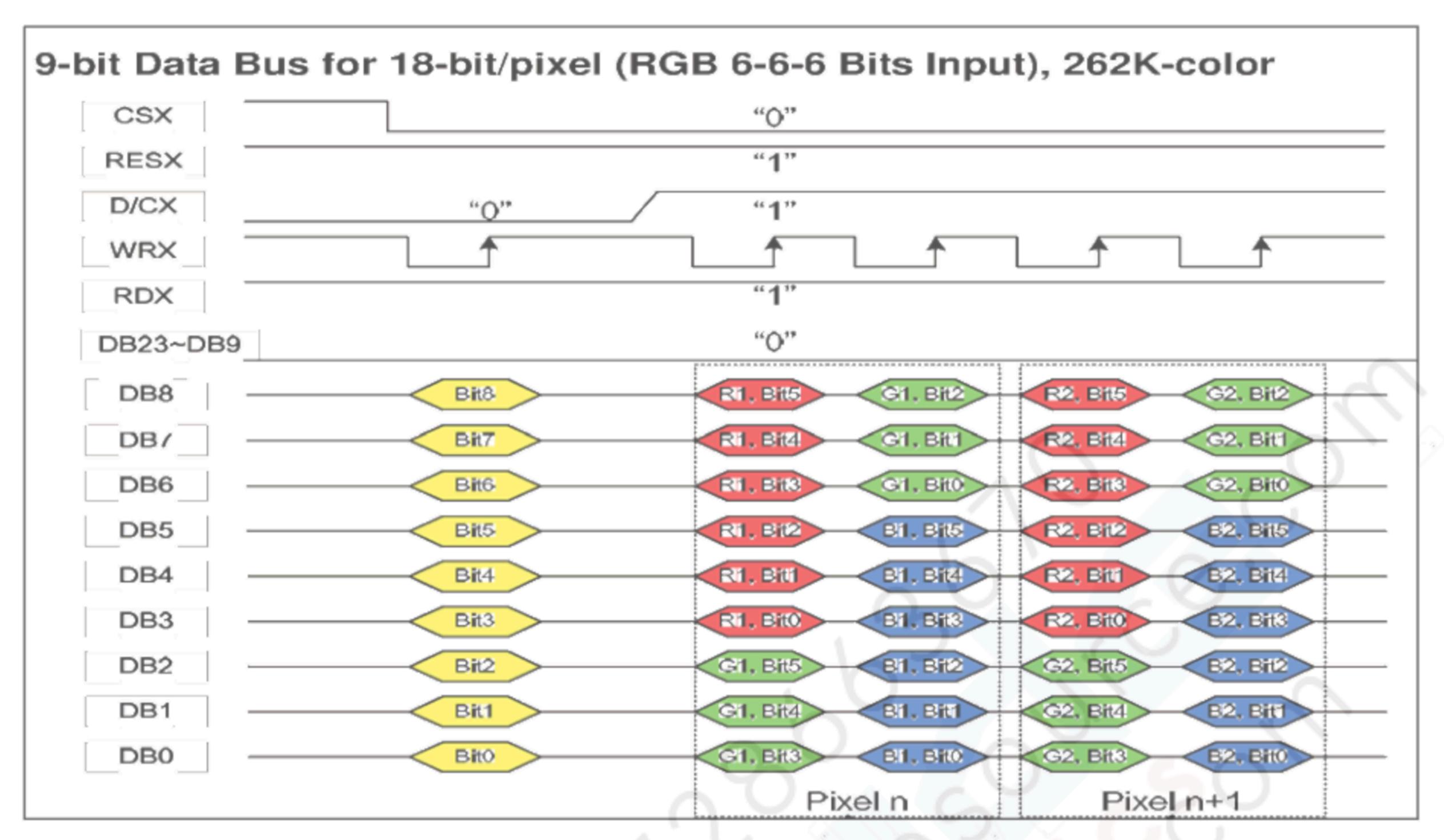

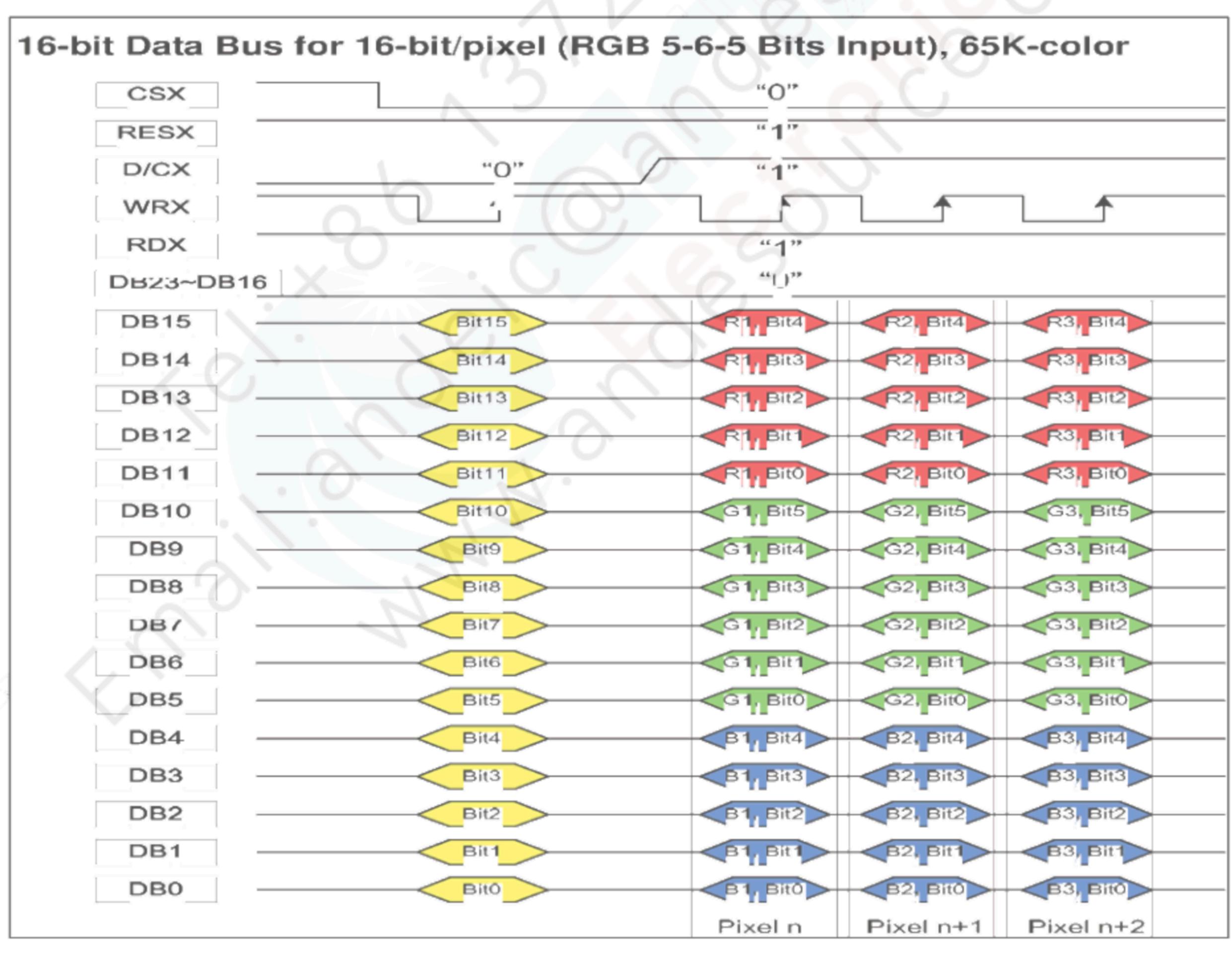

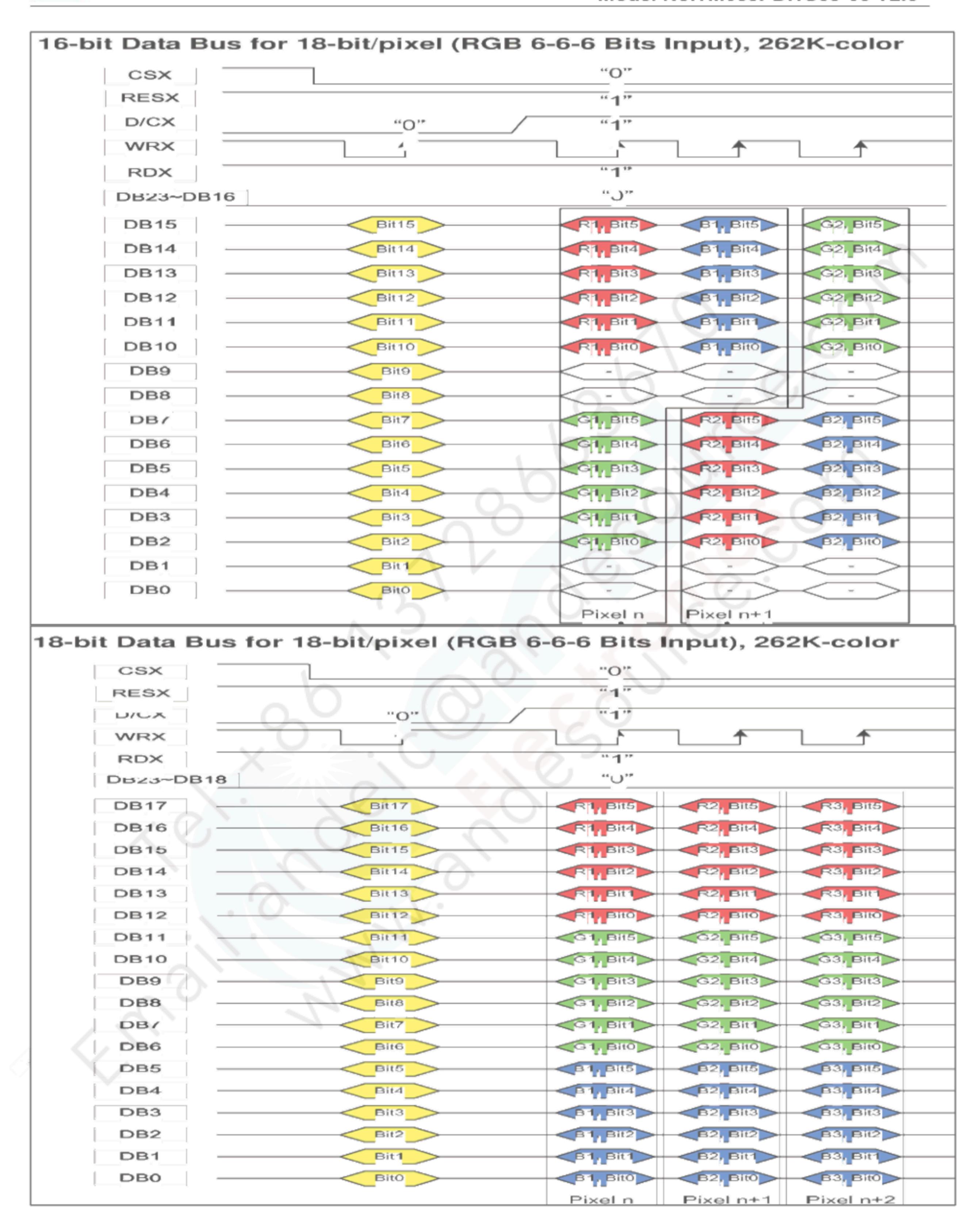

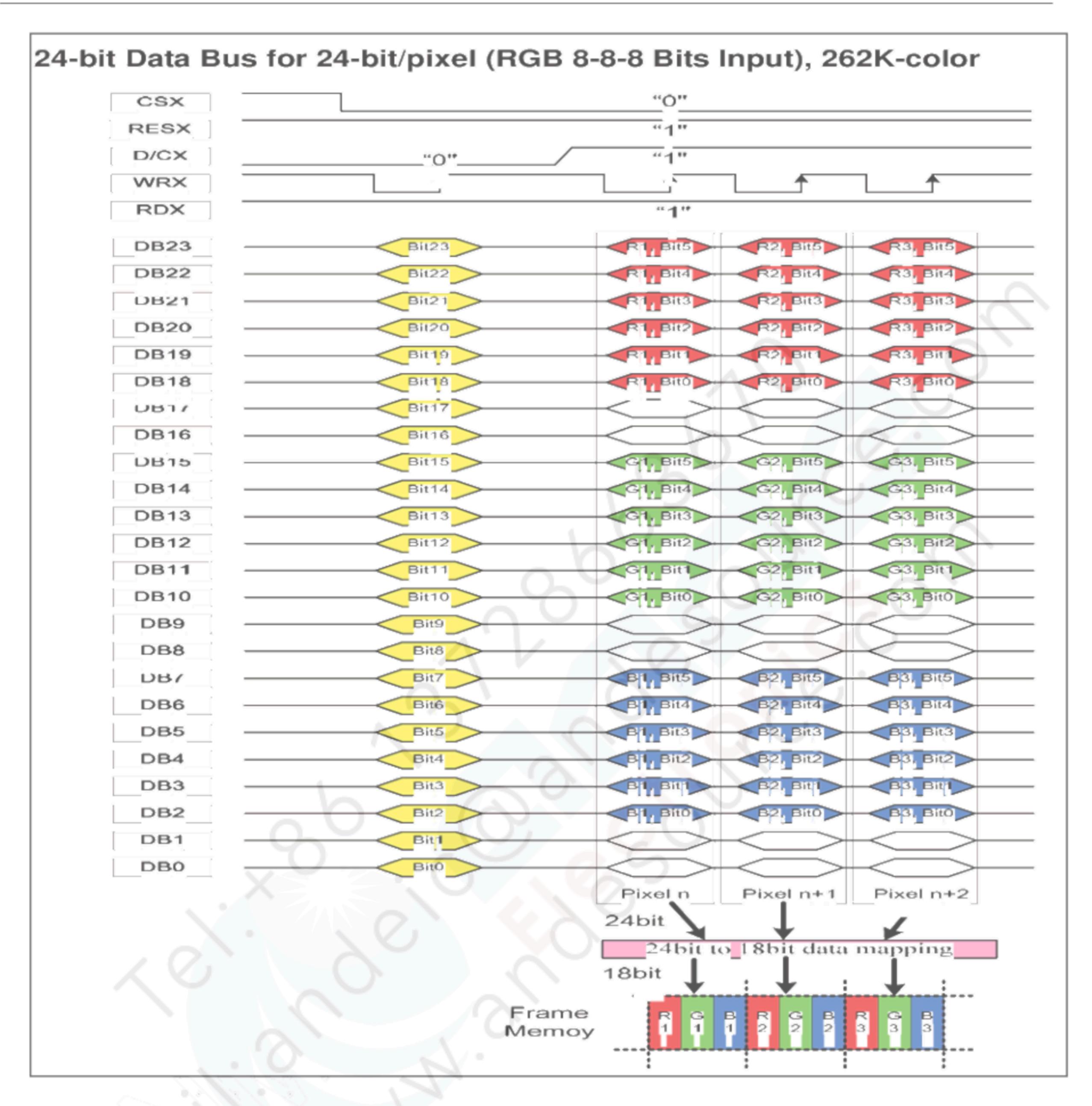

## 5.1.2 DBI Type B Data bus

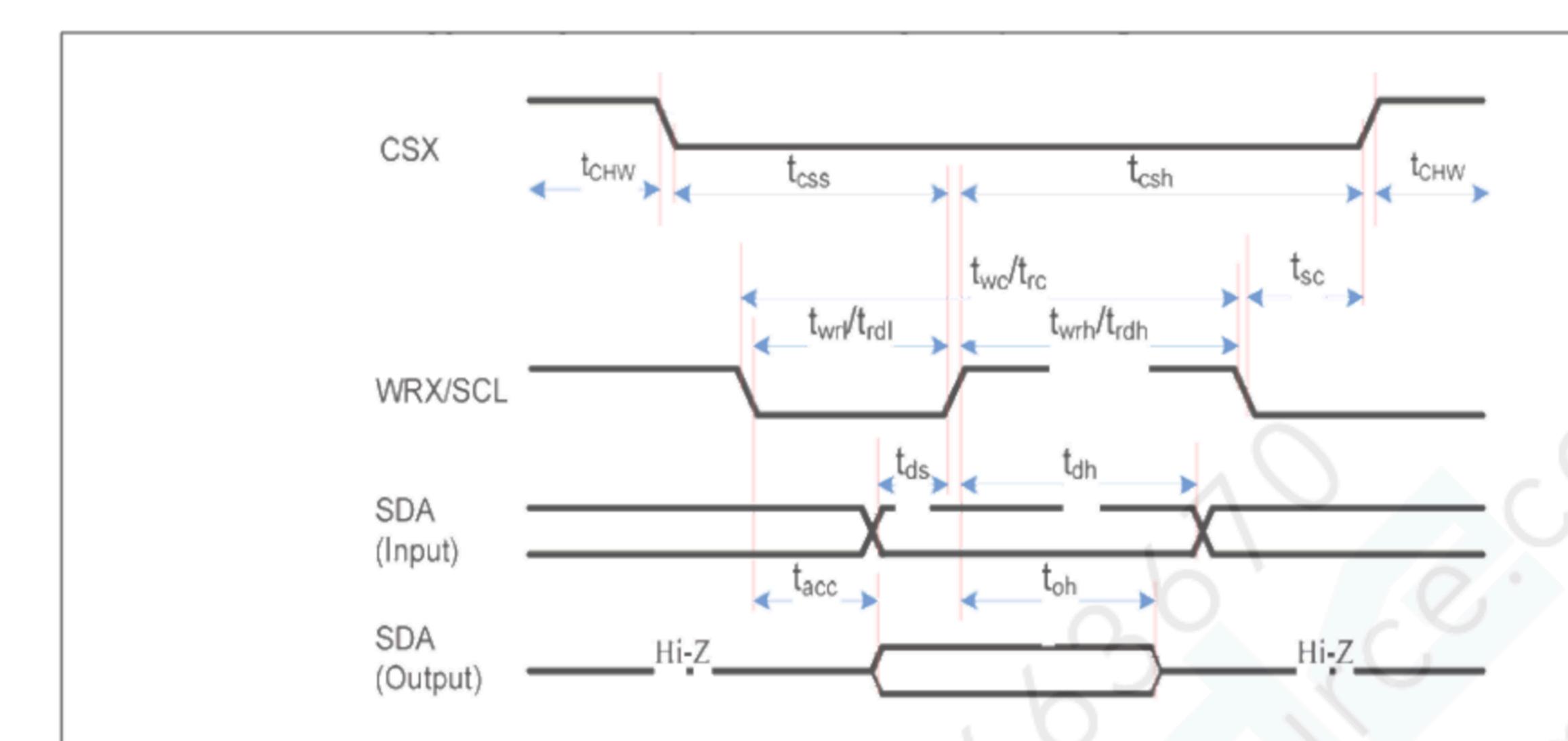

#### 5.2 3-Line SPI Interface Characteristic

| Signal              | Symbol | Parameter                    | min | max | Unit | Description        |

|---------------------|--------|------------------------------|-----|-----|------|--------------------|

|                     | tsc    | SCL-CSX                      | 15  | CO  | ns   |                    |

| 000                 | tchw   | CSX H Pulse Width            | 40  |     | ns   |                    |

| CSX                 | tcss   | Chip select time (Write)     | 60  |     | ns   |                    |

|                     | tcsh   | Chip select hold time (Read) | 65  | *   | ns   |                    |

|                     | twc    | Serial Clock Cycle (Write)   | 66  |     | ns   |                    |

|                     | twrh   | SCL H Pulse Width (Write)    | 15  | 2   | ns   |                    |

| 001                 | twrl   | SCL L Pulse Width (Write)    | 15  |     | ns   |                    |

| SCL                 | trc    | Serial Clock Cycle (Read)    | 150 | 9   | ns   |                    |

|                     | trdh   | SCL H Pulse Width (Read)     | 60  |     | ns   |                    |

|                     | trdl   | SCL L Pulse Width (Read)     | 60  |     | ns   |                    |

| SDA<br>(Input)      | tds    | Data setup time (Write)      | 10  | *   | ns   |                    |

|                     | tdh    | Data hold time (Write)       | 10  | ×   | ns   |                    |

| SDA/SDO<br>(Output) | tacc   | Access time (Read)           | 10  | 50  | ns   | For maximum CL=30p |

|                     | toh    | Output disable time (Read)   | 15  | 50  | ns   | For minimum CL=8pF |

Note: Ta = -30 to 70 °C, IOVCC = 1.65V to 3.6V, VCI = 2.5V to 3.6V, AGND = DGND = 0V, T = 10+/-0.5ns

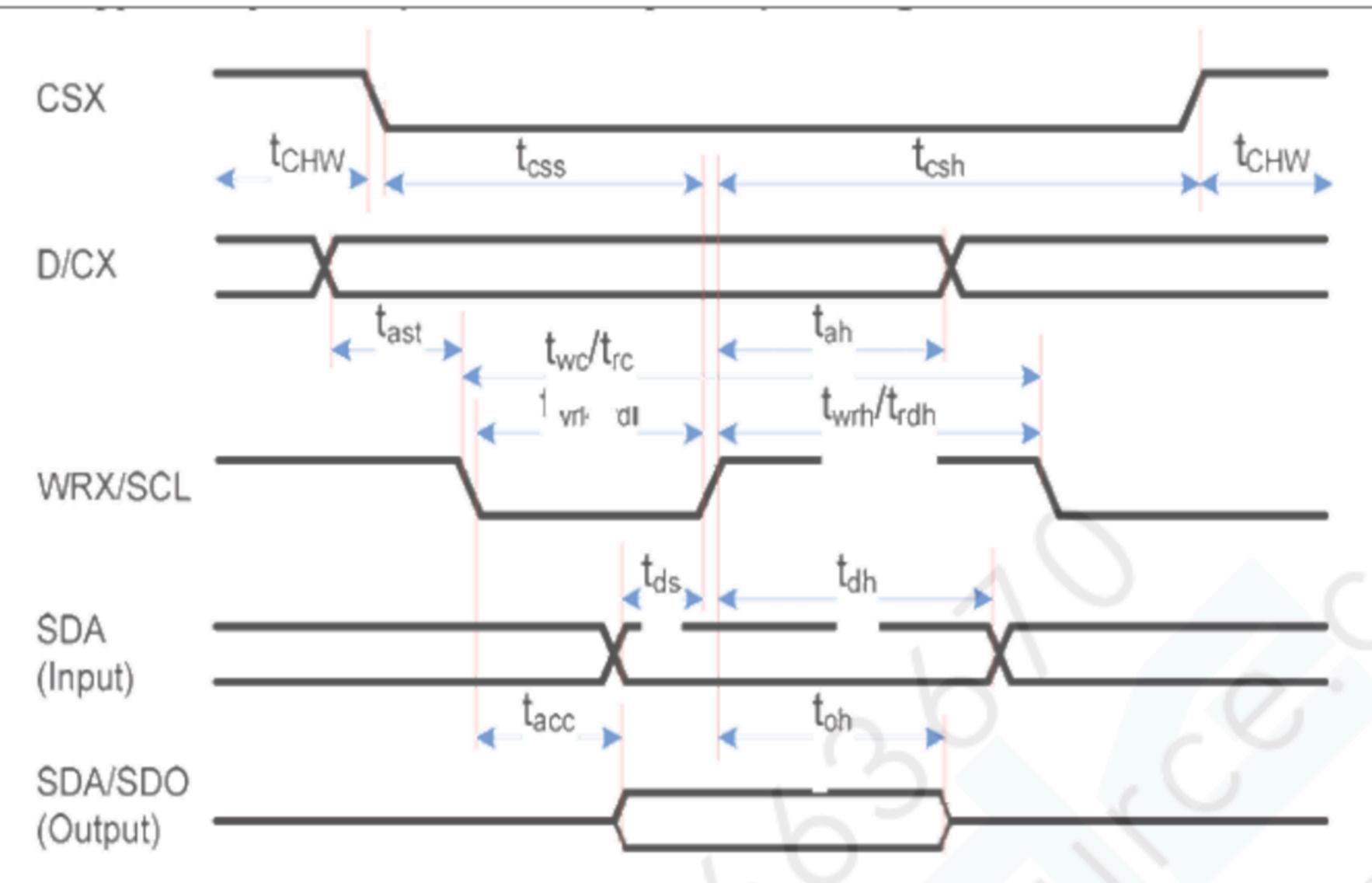

#### 5.3 4-Line SPI Interface Characteristic

| Signal   | Symbol | Parameter                    | min | max      | Unit | Description         |

|----------|--------|------------------------------|-----|----------|------|---------------------|

|          | tcss   | Chip select time (Write)     | 15  | (        | ns   |                     |

| CSX      | tcsh   | Chip select hold time (Read) | 15  |          | ns   |                     |

|          | 1CHW   | CS H pulse width             | 40  |          | ns   |                     |

|          | twc    | Serial clock cycle (Write)   | 50  |          | ns   |                     |

|          | twrh   | SCL H pulse width (Write)    | 10  |          | ns   |                     |

| 0.01     | twrl   | SCL L pulse width (Write)    | 10  |          | ns   |                     |

| SCL      | trc    | Serial clock cycle (Read)    | 150 | 1        | ns   |                     |

|          | trdh   | SCL H pulse width (Read)     | 60  | <u> </u> | ns   |                     |

|          | trdl   | SCL L pulse width (Read)     | 60  |          | ns   |                     |

| D.O.V    | tas    | D/CX setup time              | 10  |          | ns   |                     |

| D/CX     | tah    | D/CX hold time (Write/Read)  | 10  | ~        | ns   |                     |

| SDA      | tds    | Data setup time (Write)      | 10  | ~        | ns   |                     |

| (Input)  | tdh    | Data hold time (Write)       | 10  | -        | ns   |                     |

| SDA/SDO  | tacc   | Access time (Read)           | 10  | 50       | ns   | For maximum CL=30pF |

| (Output) | tod    | Output disable time (Read)   | 15  | 50       | ns   | For minimum CL=8pF  |

#### Notes:

- 1. Ta = -30 to 70 °C, IOVCC = 1.65V to 3.3V, VCI = 2.5V to 3.3V, AGND = DGND = 0V, T = 10+/-0.5ns.

- 2. Does not include signal rising and falling times.

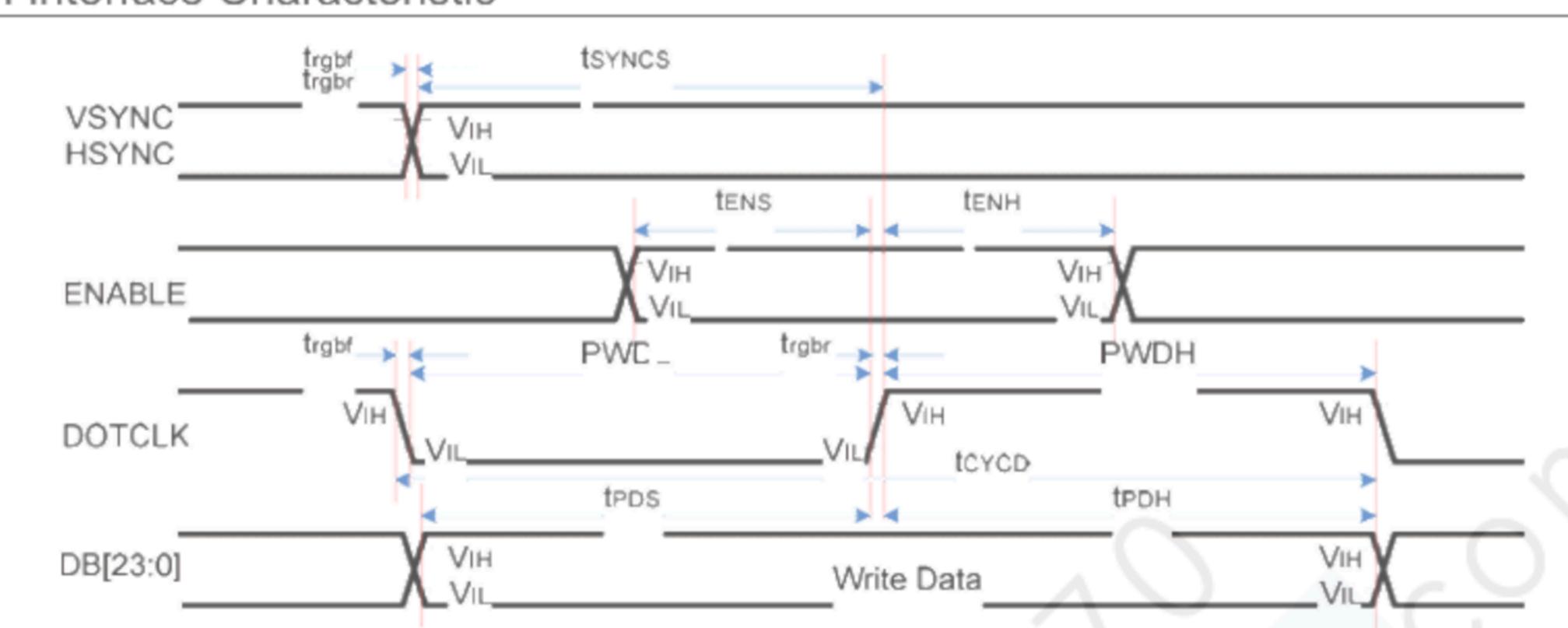

#### 5.4 DPI Interface

### 5.4.1 DPI Interface Characteristic

| Signal      | Symbol                                | Parameter                         | min  | max | Unit | Description        |

|-------------|---------------------------------------|-----------------------------------|------|-----|------|--------------------|

| VSYNC/      | Isyncs                                | VSYNC/HSYNC setup time            | 15   | - 4 | ns   |                    |

| HSYNC       | tsynch                                | VSYNC/HSYNC hold time             | 15   |     | ns   |                    |

| ENLABLE     | t <sub>ENS</sub>                      | ENABLE setup time                 | 15   |     | ns   |                    |

| ENABLE      | t <sub>ENH</sub>                      | ENABLE hold time                  | 15   | -   | ns   |                    |

| D.D. 100 01 | teos                                  | Data setup time                   | 15   |     | ns   | 16-/18-/24-bit bus |

| DB [23:0]   | t <sub>PDH</sub>                      | Data hold time                    | 15   |     | ns   | RGB interface mode |

|             | PWDH                                  | DOTCLK high-level period          | 20   |     | ns   |                    |

| DOTO! I     | PWDL                                  | DOTCLK low-level period           | 20   |     | ns   |                    |

| DOTCLK      | toyon                                 | DOTCLK cycle time                 | 50   | 7.  | ns   |                    |

|             | 1 <sub>rgbr</sub> , 1 <sub>rgbt</sub> | DOTCLK.HSYNC.VSYNC rise/fall time | A- 1 | 15  | ns   |                    |

Note: Ta = -30 to 70 °C, IOVCC = 1.65V to 3.3V, VCI = 2.5V to 3.3V, AGND = DGND = 0V

### 5.4.2 DPI Interface pixel formal

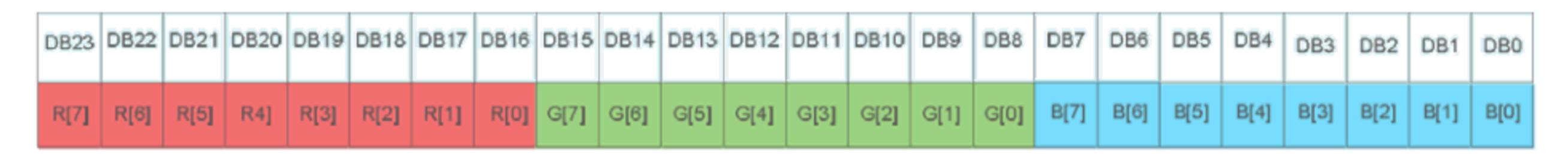

## 24-bit DPI interface connection (DB [23:0] is used): set pixel format DPI [2:0] = 3'h7

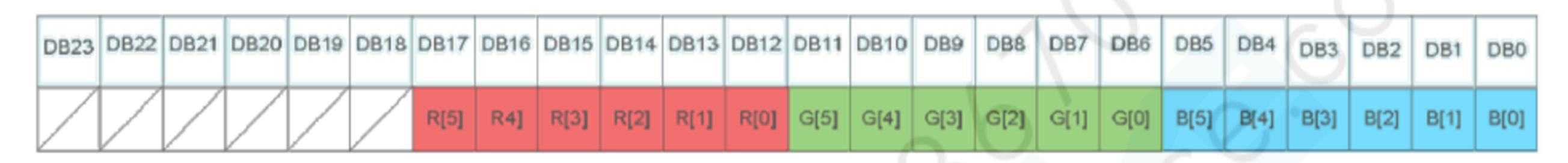

## 18-bit DPI interface connection (DB [17:0] is used): set pixel format DPI [2:0] = 3'h6

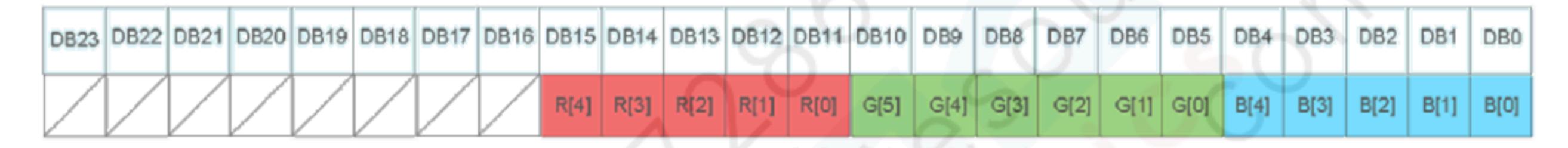

## 16-bit DPI interface connection (DB [15:0] is used); set pixel format DPI [2:0] = 3'h5

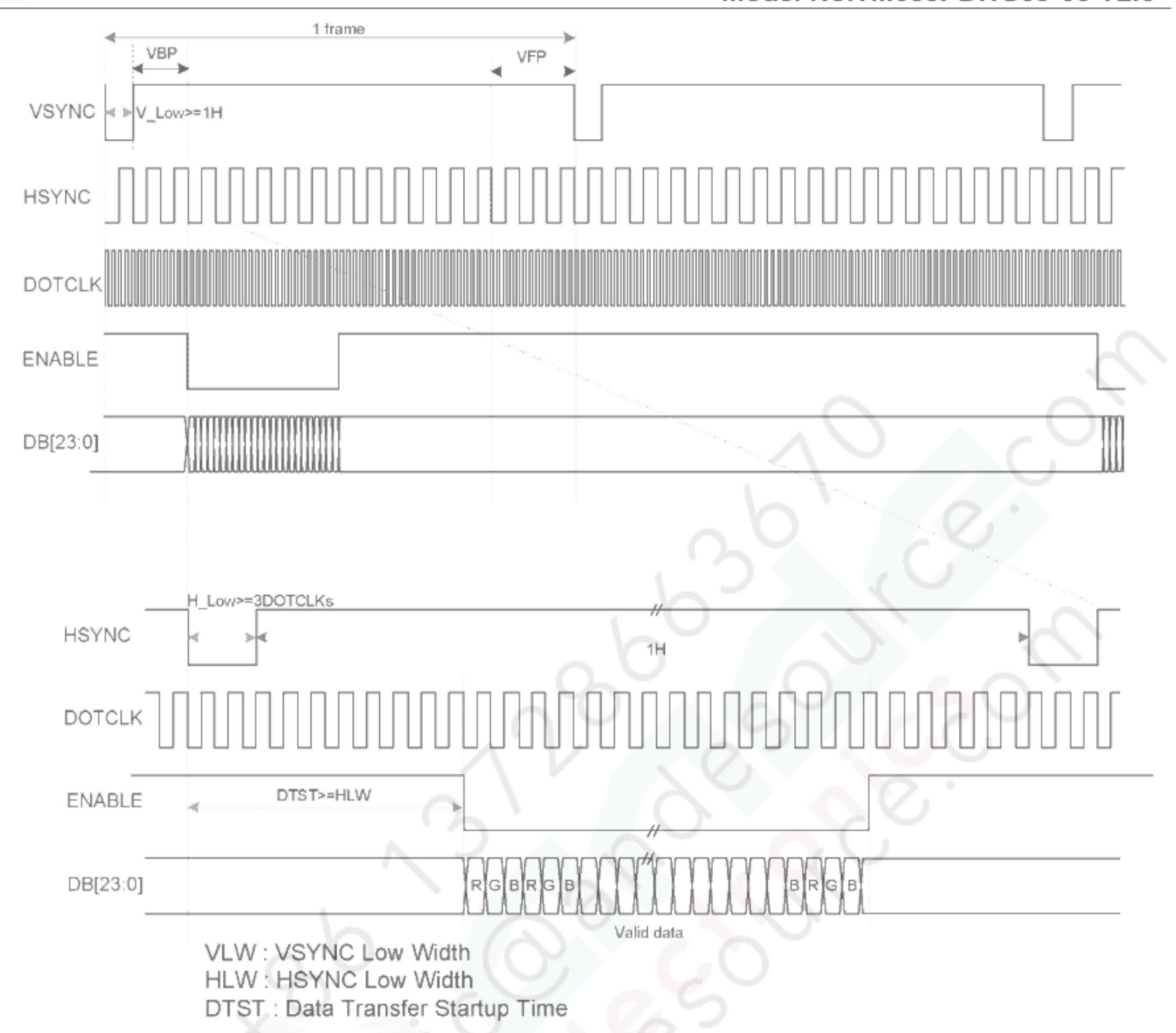

The Pixel clock (DOTCLK) runs all the time without stop. It is used to enter VSYNC, HSYNC, ENABLE and DB [23:0] states when there is a rising edge of the DOTCLK. The DOTCLK cannot be used as the internal clock for other functions of the display module.

Vertical synchronization (VSYNC) is used to indicate when a new frame of the display is received. This is low enable and its state is read to the display module by a rising edge of the DOTCLK signal.

Horizontal synchronization (HSYNC) is used to indicate when a new line of the frame is received. This is low enable and its state is read to the display module by a rising edge of the DOTCLK signal.

Data Enable (ENABLE) is used to indicate when the RGB information that should be transferred in the display is received. This is a high enable, and its state is read to the display module by a rising edge of the DOTCLK signal. DB [23:0] is used to indicate what is the information of the image that is transferred on the display (when ENABLE = 0 (low) and there is a rising edge of DOTCLK). DB [23:0] can be 0 (low) or 1 (high). These lines are read by a rising edge of the DOTCLK signal. In RGB interface modes, the input display data is written to GRAM first then outputs the corresponding source voltage according to the gray data from GRAM.

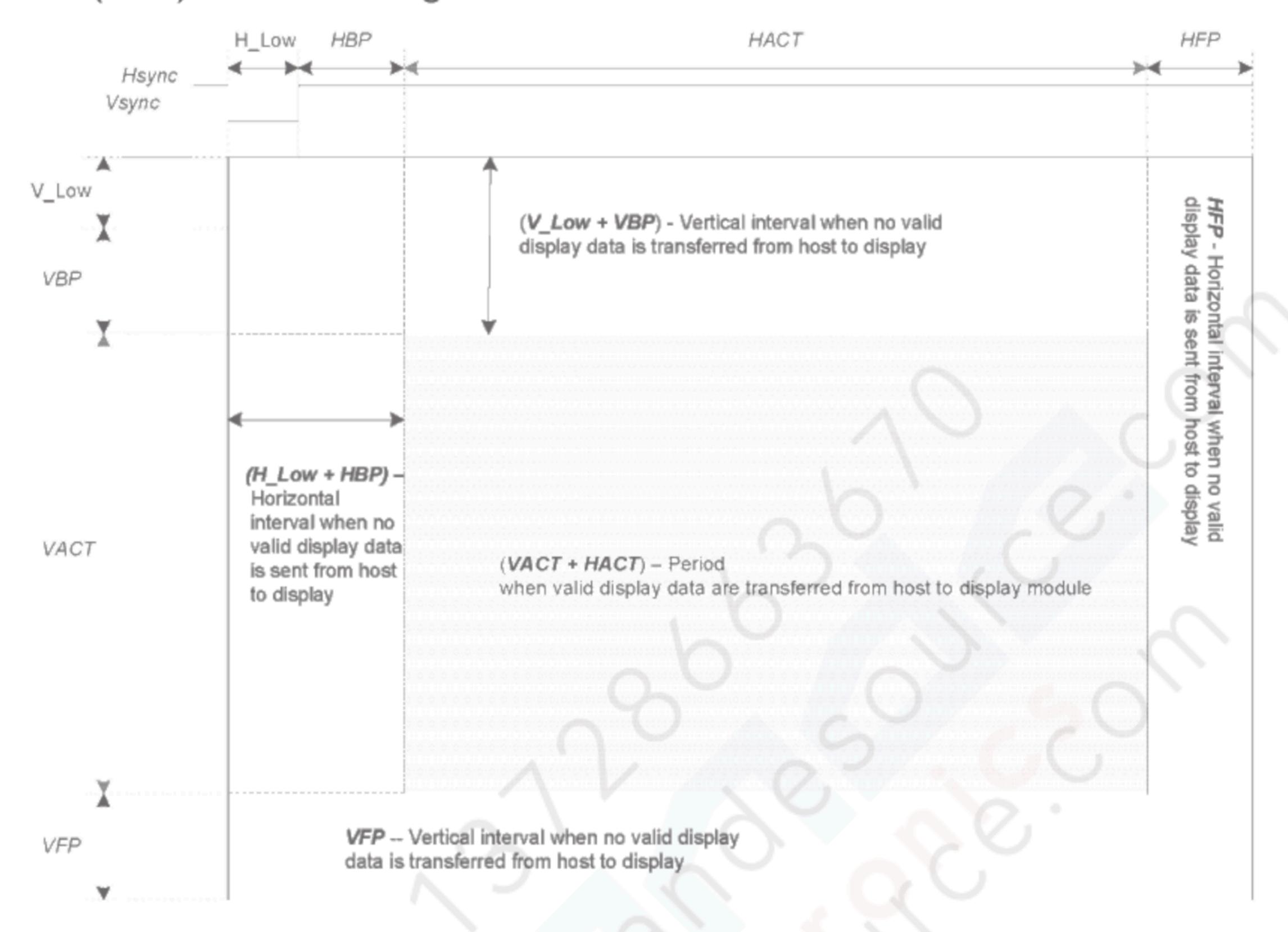

### 5.4.3 DPI(RGB) interface timing

| Parameters                 | Symbols | Min. | Тур. | Max.               | Units  |

|----------------------------|---------|------|------|--------------------|--------|

| Horizontal Synchronization | H_Low   | 3 -  |      | 11. 1              | DOTCLK |

| Horizontal Back Porch      | HBP     | 3    | ~~   | H_Low+HBP <192     | DOTCLK |

| Horizontal Front Porch     | HFP     | 3    |      | 255                | DOTCLK |

| Horizontal Address         | HACT    |      | 320  | ~                  | DOTCLK |

| Horizontal Frequency       |         |      |      | 33                 | KHz    |

| Vertical Synchronization   | V_Low   | 1    | -    |                    | Line   |

| Vertical Back Porch        | VBP     | 2    | ×    | V_Low+VBP+VFP < 32 | Line   |

| Vertical Front Porch       | VFP     | 2    | 14.  |                    | Line   |

| Vertical Address           | VACT    | ŭ    | 480  | ~                  | Line   |

| Vertical Frequency         |         | 60   |      | 70                 | Hz     |

| DOTCLK cycle               |         | 100  |      | 50                 | ns     |

| DOTCLK Frequency           |         | 10   | 1-   | 20                 | MHz    |

Example: DOTCLK = 20Mhz, TE=70Hz, V\_Low+VBP=2, VFP=2, H\_Low+HBP=100, HFP=170.

Note: VBP[4:0]/HBP[7:0] (Blanking Porch Control, RB5h) define as follows:

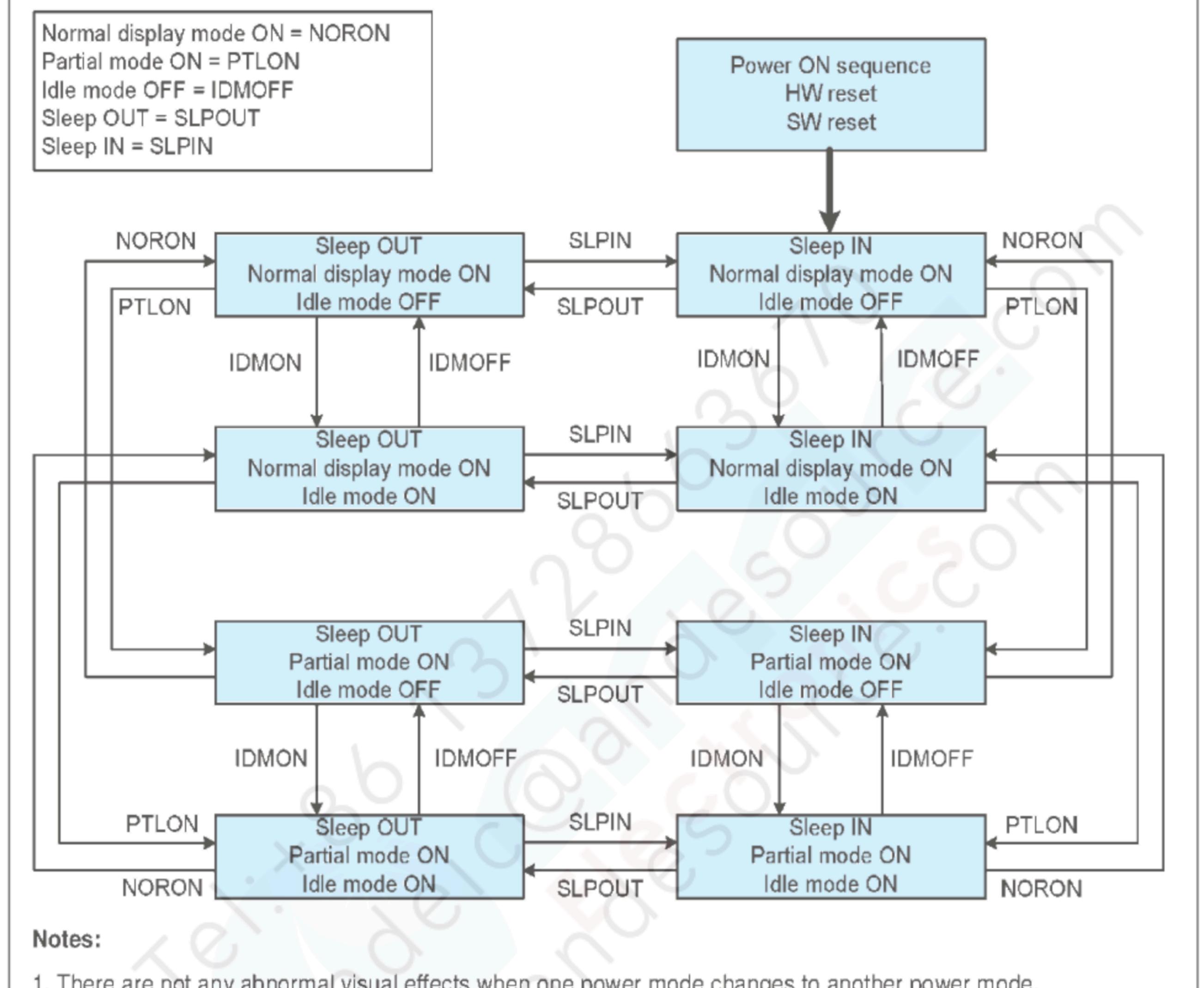

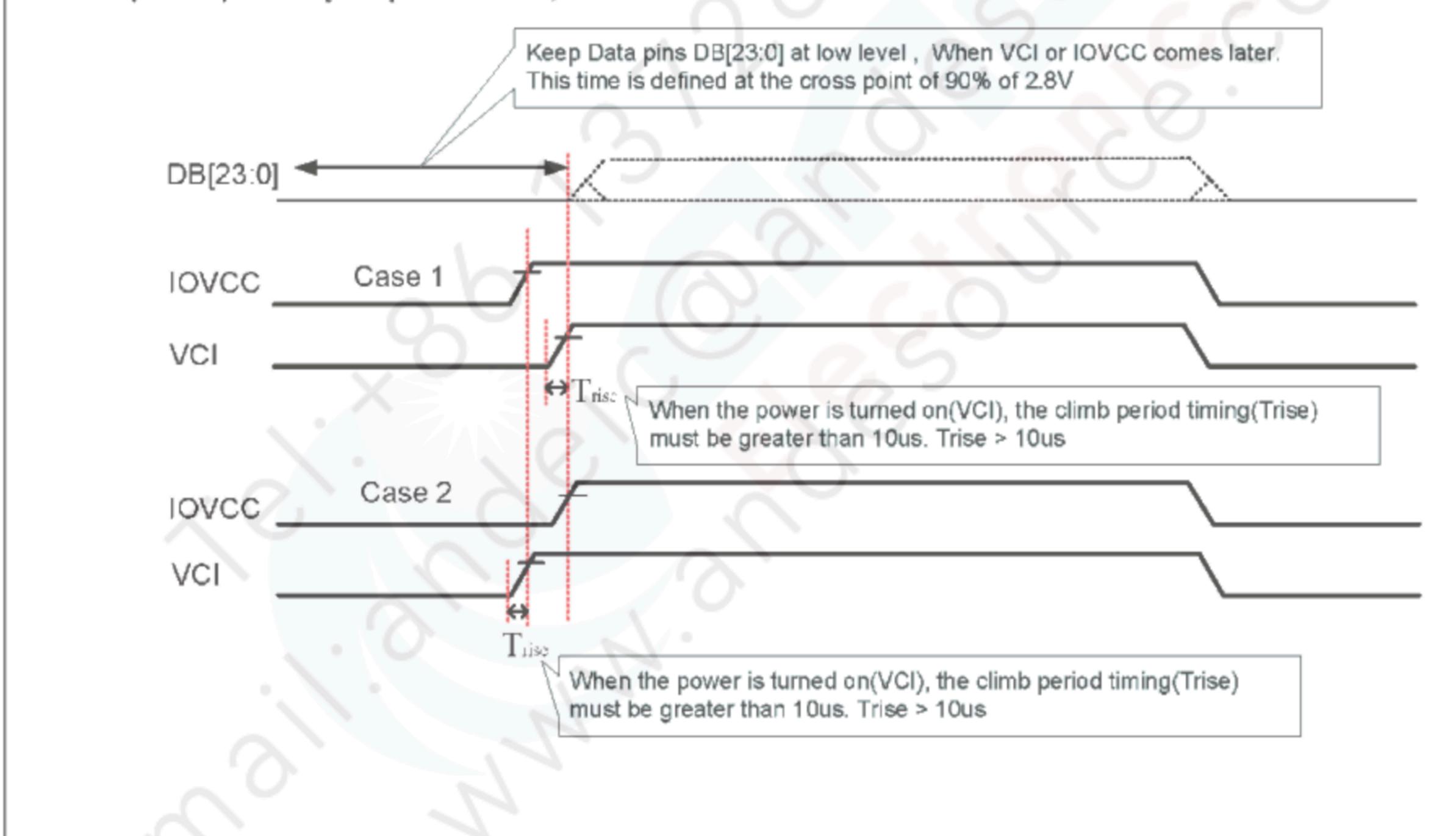

### 5.5 Power ON/OFF Sequence

- 1. There are not any abnormal visual effects when one power mode changes to another power mode.

- 2. There is not any limitation, which is not specified by users, when one power mode changes to another power mode.

IOVCC and VCI can be applied or powered down in any order. During the Power Off sequence, if the LCD is in the Sleep Out mode, VCI and IOVCC must be powered down with a minimum of 120msec. If the LCD is in the Sleep In mode, VCI and IOVCC can be powered down with a minimum of 0msec after the RESX has been released.

CSX can be applied at any time or can be permanently grounded. RESX has high priority over CSX.

#### Notes:

- 1. There will be no damage to the ILI9488 if the power sequences are not met.

- 2. There will be no abnormal visible effects on the display panel during the Power On/Off Sequence.

- There will be no abnormal visible effects on the display between the end of the Power On Sequence and before

receiving the Sleep Out command, and also between receiving the Sleep In command and the Power Off

Sequence.

- 4. If the RESX line is not steadily held by the host during the Power On Sequence as defined in Sections 11.1 and 11.2, then it will be necessary to apply the Hardware Reset (RESX) after the completion of the Host Power On Sequence to ensure correct operations. Otherwise, all the functions are not guaranteed.

- 5. When the power is turned on, the climb period timing(Trise) must be greater than 10us.

- 6. Keep data pins DB[23:0] at low level, when VCI or IOVCC comes later

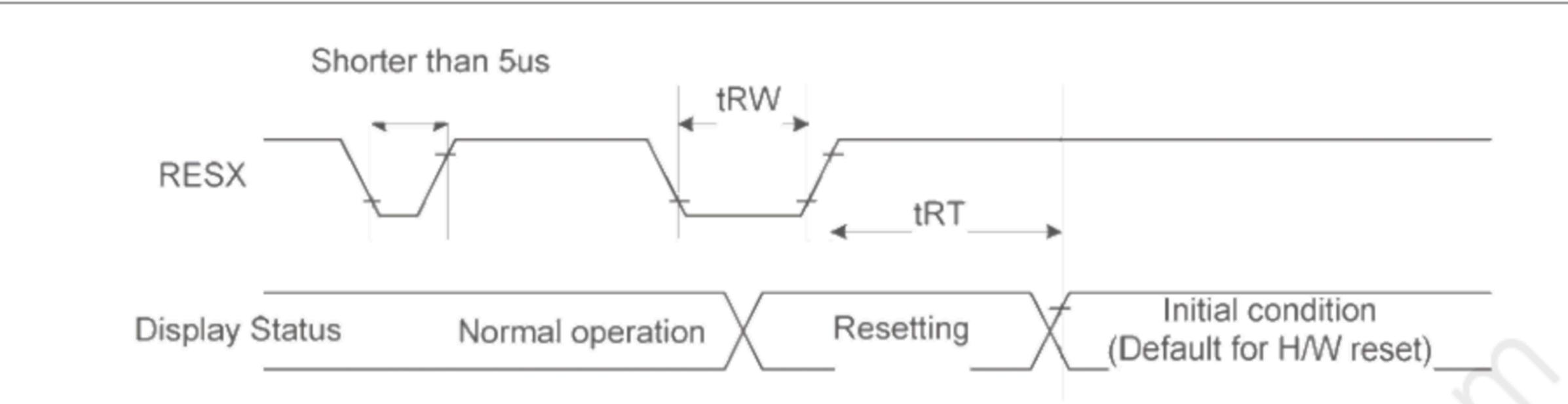

### 5.6 Reset timing

Table 39: Reset Timing

| Signal | Symbol | Parameter            | Min | Max              | Unit |

|--------|--------|----------------------|-----|------------------|------|

|        | tRW    | Reset pulse duration | 10  |                  | uS   |

| RESX   | 457    |                      |     | 5 (note 1,5)     | mS   |

|        | tRT    | Reset cancel         |     | 120 (note 1,6,7) | mS   |

#### Notes:

- The reset cancel also includes the required time for loading ID bytes, VCOM setting and other settings from the EEPROM to registers. After a rising edge of RESX, this loading is done within 5 ms after the H/W reset cancel (tRT).

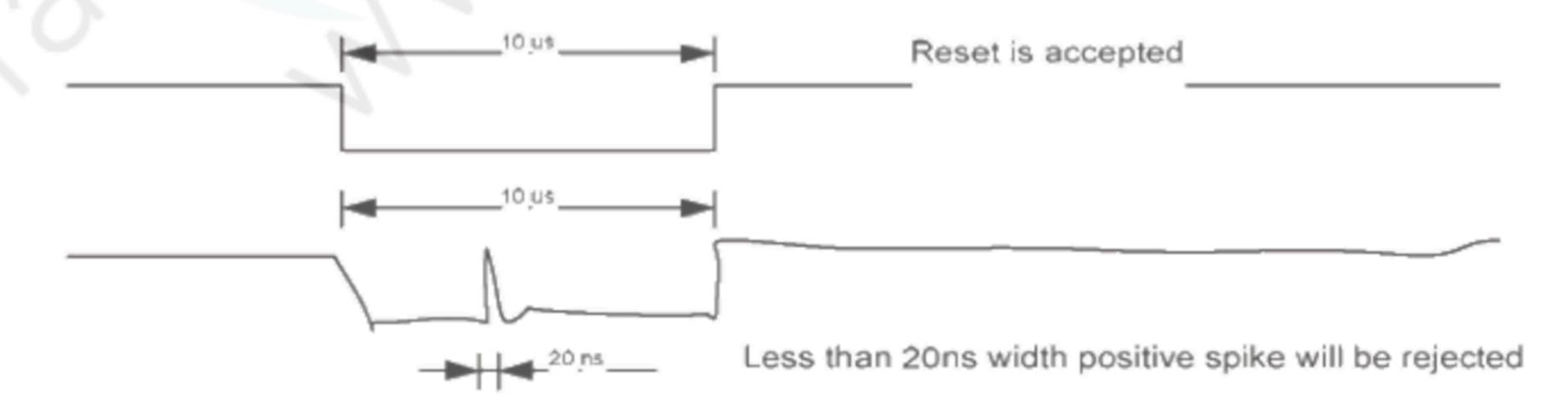

- According to the Table 40, a spike due to an electrostatic discharge on the RESX line does not cause irregular system reset.

Table 40: Reset Description

| RESX Pulse          | Action         |  |

|---------------------|----------------|--|

| Shorter than 5us    | Reset Rejected |  |

| Longer than 9us     | Reset          |  |

| Between 5us and 9us | Reset starts   |  |

- During the Reset period, the display will be blanked (When Reset starts in the Sleep Out mode, the display will

enter the blanking sequence in at least 120 ms. The display remains the blank state in the Sleep In mode.) and

then return to the default condition for the Hardware Reset.

- 4. Spike Rejection can also be applied during a valid reset pulse, as shown below:

Figure 137: Positive Noise Pulse during Reset Low

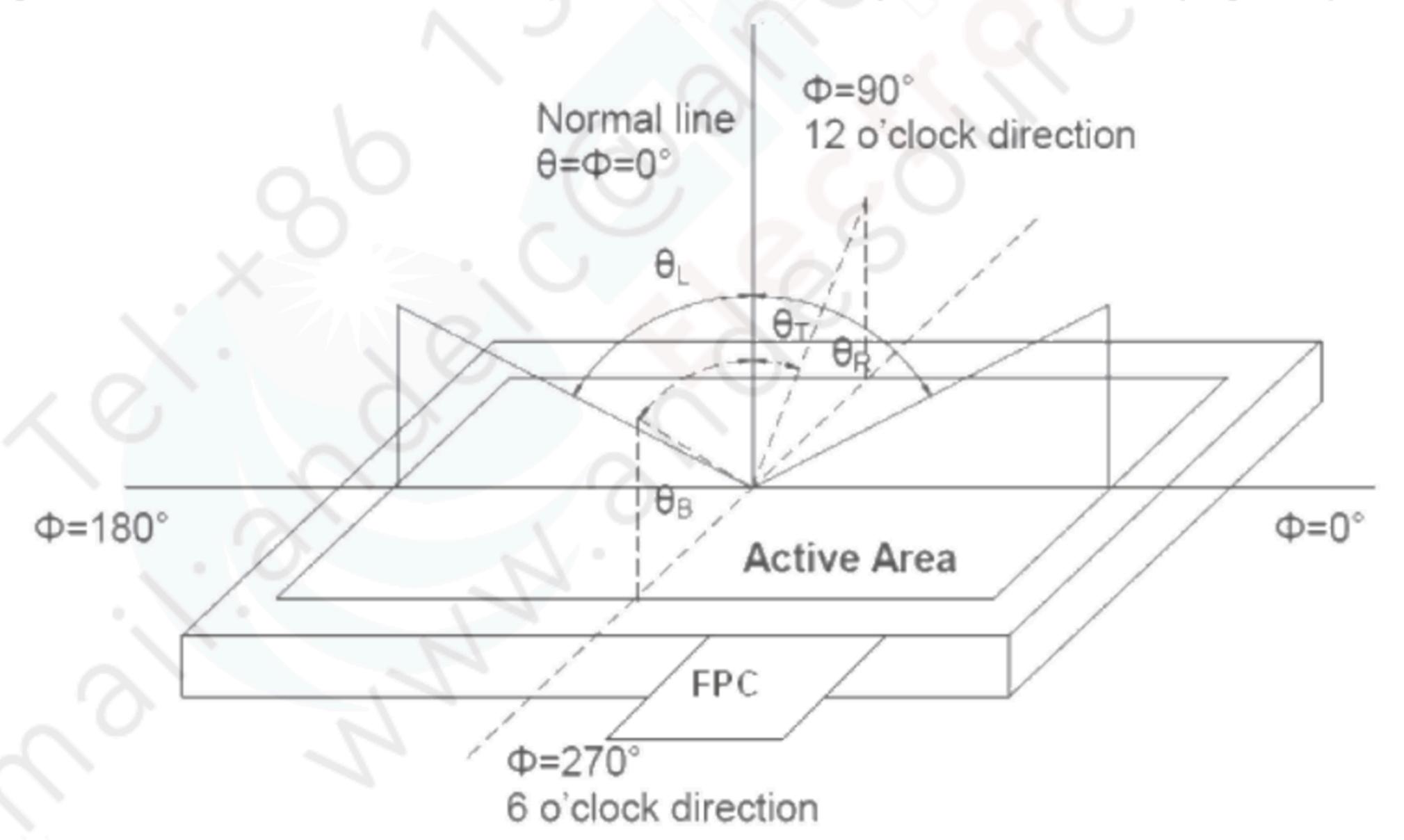

# 6 Optical Characteristics

| ltem           |       | Symbol           | Condition       | Min | Тур   | Max | Unit              | Remark   |

|----------------|-------|------------------|-----------------|-----|-------|-----|-------------------|----------|

|                |       | θТ               |                 | 60  | 70    |     |                   | Note2,3  |

| \              |       | θВ               | CD > 10         | 50  | 60    |     | Dograo            |          |

| View Angles    |       | θL               | CR≧10           | 60  | 70    |     | Degree            |          |

|                |       | θR               |                 | 60  | 70    |     |                   |          |

| Contrast Ratio | )     | CR               | θ=0°            | 400 | 500   |     |                   | Note 3   |

| Doononeo Tim   |       | Ton              | 25°C            |     | 25    | 25  | ma                | Note 4   |

| Response Time  |       | T <sub>OFF</sub> | 25°C            |     | 25    | 35  | ms                | Note 4   |

|                | White | X                | Backlight is on | - ( | 0.286 |     | +/-0.05           | Note 1,5 |

|                |       | У                |                 |     | 0.304 |     |                   |          |

|                | Red   | X                |                 |     | 0.608 | - / |                   | Note 1,5 |

| Chromaticity   |       | У                |                 | - 3 | 0.336 |     |                   |          |

| Cilioniaticity | Groon | Х                |                 | -   | 0.341 | - 0 |                   | Note 1,5 |

|                | Green | у                |                 |     | 0.604 |     |                   |          |

|                | Divio | X                |                 |     | 0.146 | -   |                   | Note 1,5 |

|                | Blue  | у                |                 | -   | 0.073 | -   |                   |          |

| Uniformity     |       | U                |                 |     | 80    | _   | %                 | Note 6   |

| NTSC           |       |                  |                 |     | 60    | -   | %                 | Note 5   |

| Luminance      |       | L                |                 | 250 | _     | _   | cd/m <sup>2</sup> | Note 7   |

### Test Conditions:

- 1. ILED= 20 mA, and the ambient temperature is 25°C.

- 2. The test systems refer to Note 1 and Note 2.

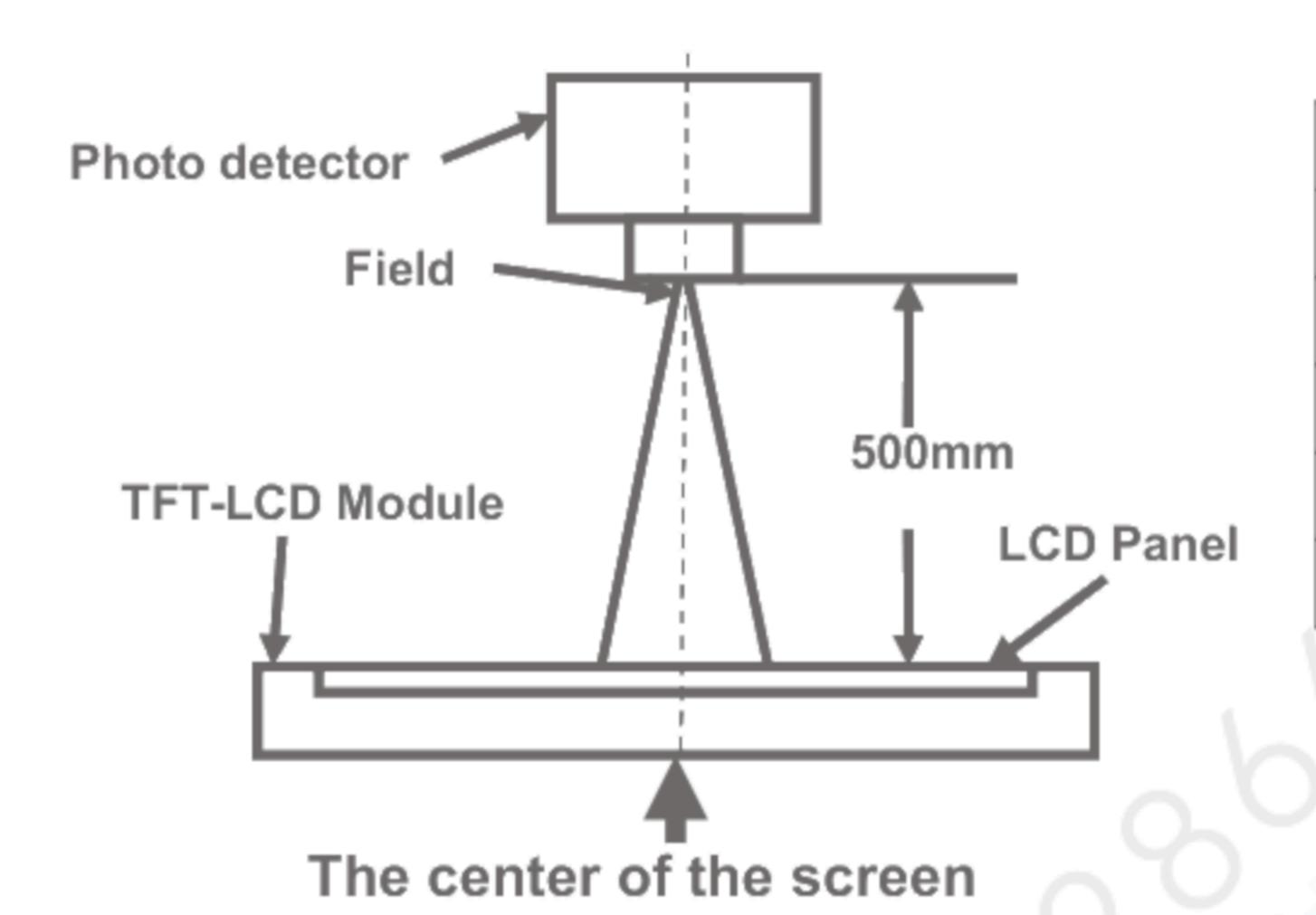

Note 1: Definition of optical measurement system.

The optical characteristics should be measured in dark room. After 5 Minutes operation, the optical properties are measured at the center point of the LCD screen. All input terminals LCD panel must be ground when measuring the center area of the panel.

| ltem           | Photo detector | Field |  |

|----------------|----------------|-------|--|

| Contrast Ratio |                |       |  |

| Luminance      | CD 2A          | 1°    |  |

| Chromaticity   | SR-3A          |       |  |

| Lum Uniformity |                |       |  |

| Response Time  | BM-7A          | 2°    |  |

Note 2: Definition of viewing angle range and measurement system.

viewing angle is measured at the center point of the LCD by CONOSCOPE(ergo-80).

Note 3: Definition of contrast ratio

Contrast ratio (CR) =  $\frac{\text{Luminance measured when LCD is on the "White" state}}{\text{Luminance measured when LCD is on the "Black" state}}$

"White state ": The state is that the LCD should drive by Vwhite.

"Black state": The state is that the LCD should drive by Vblack.

Vwhite: To be determined Vblack: To be determined.

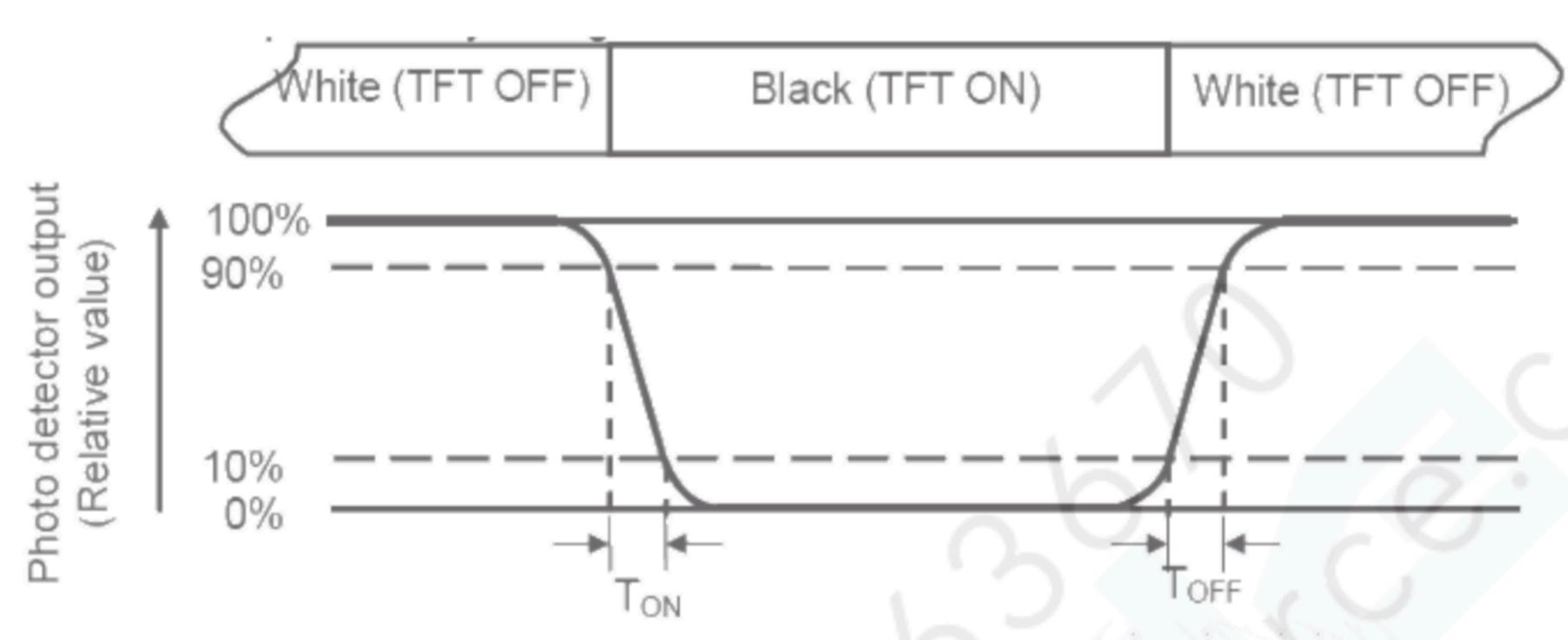

### Note 4: Definition of Response time

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time (T<sub>ON</sub>) is the time between photo detector output intensity changed from 90% to 10%. And fall time (T<sub>OFF</sub>) is the time between photo detector output intensity changed from 10% to 90%.

Note 5: Definition of color chromaticity (CIE1931)

Color coordinates measured at center point of LCD.

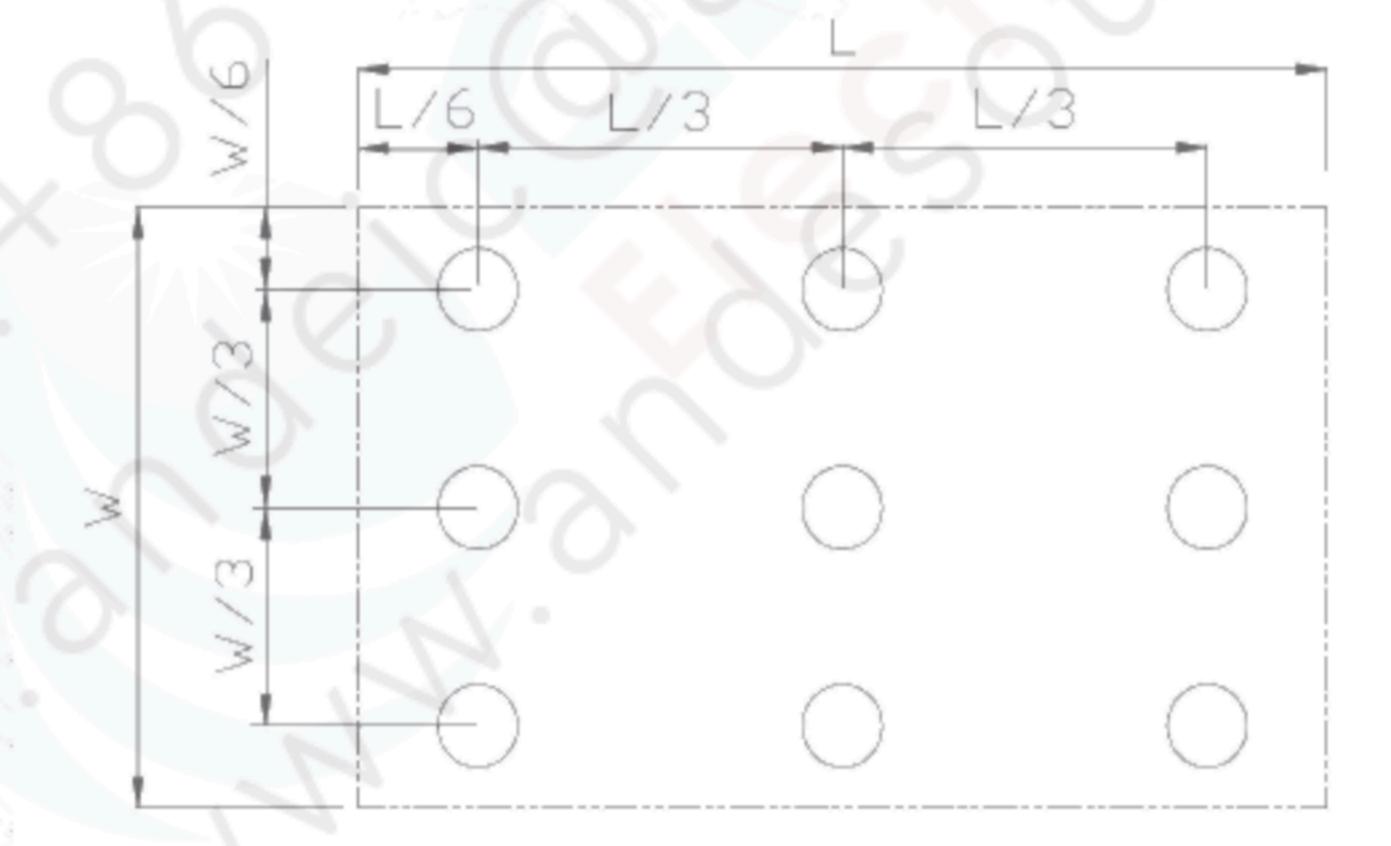

### Note 6: Definition of Luminance Uniformity

Active area is divided into 9 measuring areas (Refer Fig. 2). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity (U) = Lmin/Lmax

L----- Active area length W----- Active area width

Lmax: The measured Maximum luminance of all measurement position.

Lmin: The measured Minimum luminance of all measurement position.

#### Note 7: Definition of Luminance:

Measure the luminance of white state at center point.

# 7 Environmental / Reliability Test

| No | Test Item                                  | Condition                                                                                                                                           | Remarks                                                                               |

|----|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 1  | High Temperature<br>Operation              | Ts=+70°C, 240hrs                                                                                                                                    | Note1<br>IEC60068-2-1,GB2423.2                                                        |

| 2  | Low Temperature<br>Operation               | Ta=-20℃, 240hrs                                                                                                                                     | IEC60068-2-1<br>GB2423.1                                                              |

| 3  | High Temperature<br>Storage                | Ta=+80°C, 240hrs                                                                                                                                    | IEC60068-2-1<br>GB2423.1                                                              |

| 4  | Low Temperature<br>Storage                 | Ta=-30℃, 240hrs                                                                                                                                     | IEC60068-2-1<br>GB2423.1                                                              |

| 5  | High Temperature and Humidity Operation    | Ta=+60°C, 90% RH 240 hours                                                                                                                          | Note2<br>IEC60068-2-78<br>GB/T2423.3                                                  |

| 6  | Thermal Shock (non-operation)              | -30°C 30 min~+70°C 30 min,<br>Change time:5min, 20 Cycles                                                                                           | Start with cold temperature,<br>End with high temperature,<br>IEC60068-2-14,GB2423.22 |

| 7  | Electro Static<br>Discharge<br>(Operation) | C=150pF, R=330 <sub>¬</sub> , 5points/panel<br>Air:±8KV, 5times;<br>Contact:±4KV, 5 times;<br>(Environment: 15°C~35°C,<br>30%~60%, 86Kpa~106Kpa)    | IEC61000-4-2<br>GB/T17626.2                                                           |

| 8  | Vibration<br>(Non-operation)               | Frequency range:10~55Hz,<br>Stroke:1.5mm<br>Sweep:10Hz~55Hz~10Hz 2 hours<br>for each direction of X.Y.Z.<br>(6 hours for total) (Package condition) | IEC60068-2-6<br>GB/T2423.10                                                           |

| 9  | Shock<br>(Non-operation)                   | 60G 6ms, ±X,±Y,±Z 3times, for each direction                                                                                                        | IEC60068-2-27<br>GB/T2423.5                                                           |

| 10 | Package<br>Drop Test                       | Height:80 cm,<br>1 corner, 3 edges, 6 surfaces                                                                                                      | IEC60068-2-32<br>GB/T2423.8                                                           |

Note1: Ts is the temperature of panel's surface.

Note2: Ta is the ambient temperature of sample.

Note3: Before cosmetic and function test, the product must have enough recovery time, at least 2 hours at room temperature.

Note 4: In the standard condition, there shall be no practical problem that may affect the display function. After the reliability test, the product only guarantees operation, but don't guarantee all of the cosmetic specification.

## 8 Mechanical Drawing

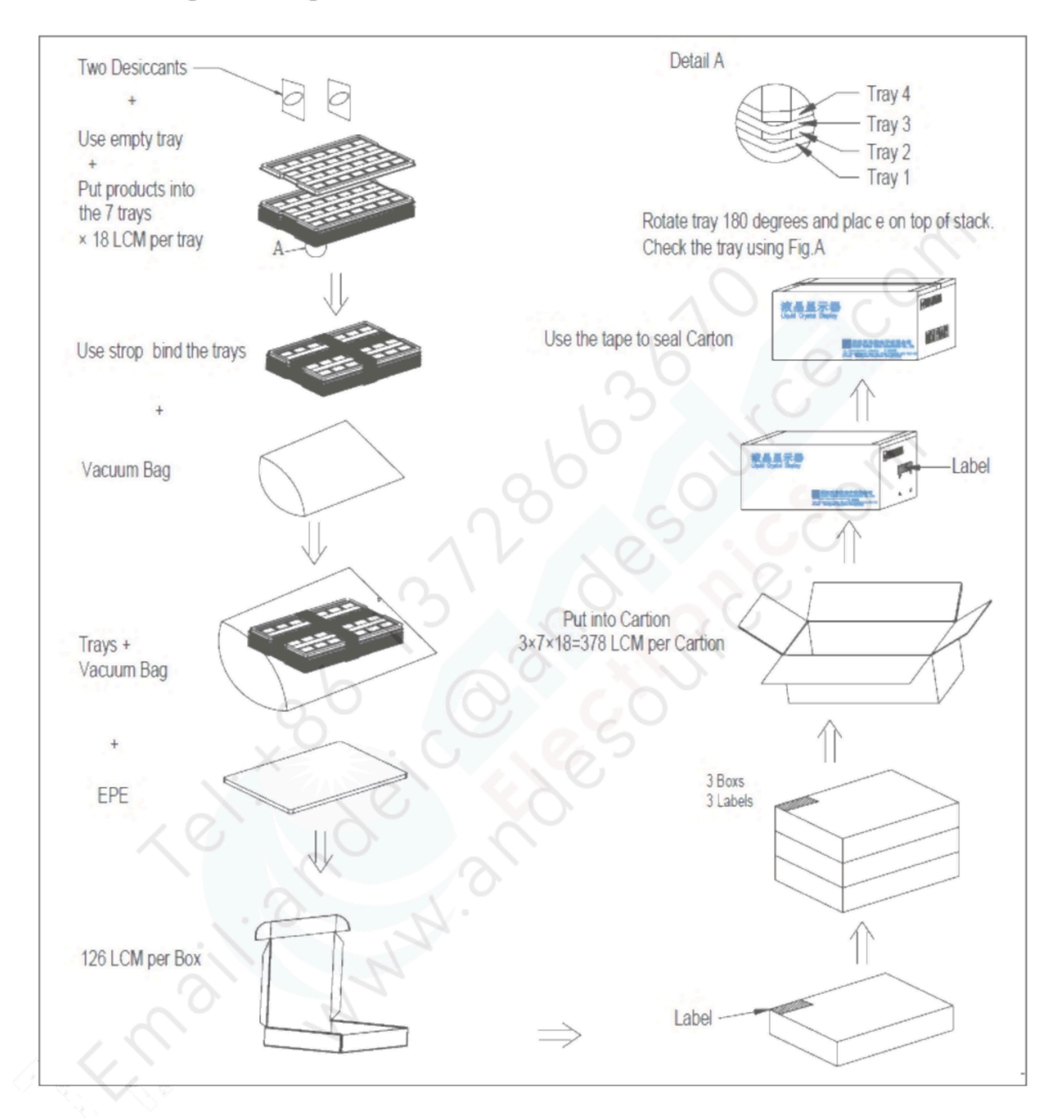

# 9 Packing Drawing

## 10 Precautions for Use of LCD Modules

- 10.1 Handling Precautions

- 10.1.1 The display panel is made of glass. Do not subject it to a mechanical shock by dropping it from a high place, etc.

- 10.1.2 If the display panel is damaged and the liquid crystal substance inside it leaks out, be sure not to get any in your mouth, if the substance comes into contact with your skin or clothes, promptly wash it off using soap and water.

- 10.1.3 Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

- 10.1.4 The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarizer carefully.

- 10.1.5 If the display surface is contaMinated, breathe on the surface and gently wipe it with a soft dry cloth. If still not completely clear, moisten cloth with one of the following solvents:

- Isopropyl alcohol

- Ethyl alcohol

Solvents other than those mentioned above may damage the polarizer. Especially, do not use the following:

- Water

- Ketone

- Aromatic solvents

- 10.1.6 Do not attempt to disassemble the LCD Module.

- 10.1.7 If the logic circuit power is off, do not apply the input signals.

- 10.1.8 To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

- 10.1.8.1 Be sure to ground the body when handling the LCD Modules.

- 10.1.8.2 Tools required for assembly, such as soldering irons, must be properly ground.

- 10.1.8.3 To reduce the amount of static electricity generated, do not conduct assembly and other work under dry conditions.

- 10.1.8.4 The LCD Module is coated with a film to protect the display surface. Be care when peeling off this protective film since static electricity may be generated.

- 10.2 Storage precautions

- 10.2.1 When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps.

- 10.2.2 The LCD modules should be stored under the storage temperature range. If the LCD modules will be stored for a long time, the recommend condition is:

- Temperature : 0°C ~ 40°C Relatively humidity: ≤80%

- 10.2.3 The LCD modules should be stored in the room without acid, alkali and harmful gas.

- 10.3 Transportation Precautions

- 10.3.1 The LCD modules should be no falling and violent shocking during transportation, and also should avoid excessive press, water, damp and sunshine.